# [Hardware]

# **Contents**

| 1.1 Appearance of Main Unit                                               | H1-1  |

|---------------------------------------------------------------------------|-------|

| 1.2 Appearance of Expander/Module                                         | H1-2  |

| 1.3 Appearance of Communication Expansion Module                          | H1-4  |

| 1.4 List of FBS-PLC Models                                                | H1-5  |

| 1.5 Specifications of Main Unit                                           | H1-7  |

| 1.6 Environmental Specifications                                          | H1-8  |

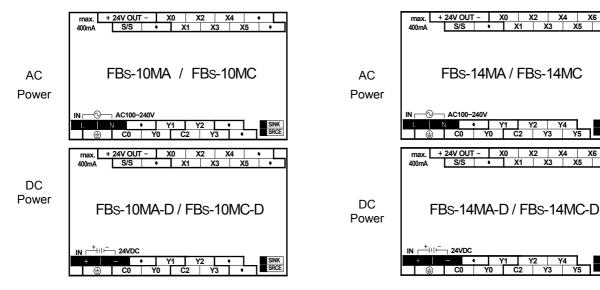

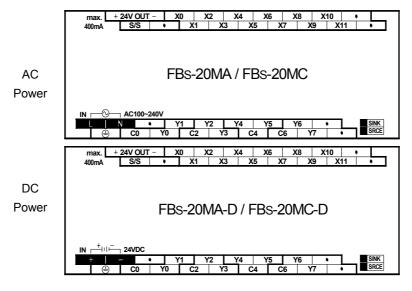

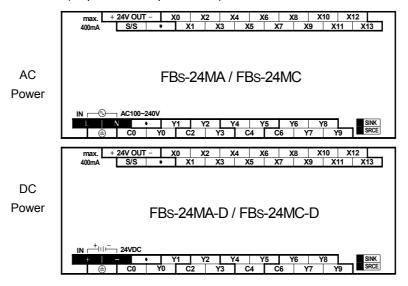

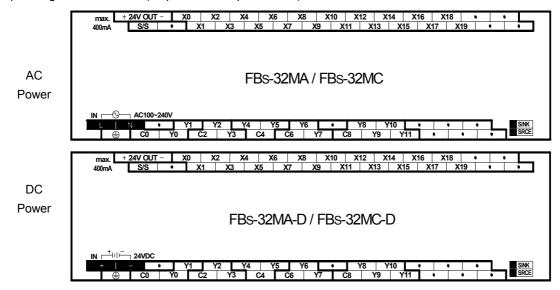

| 1.7 Connection Diagrams of Various Models                                 | H1-9  |

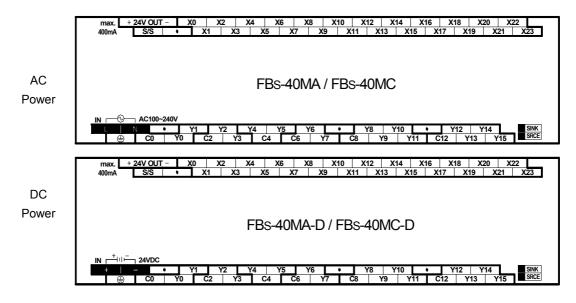

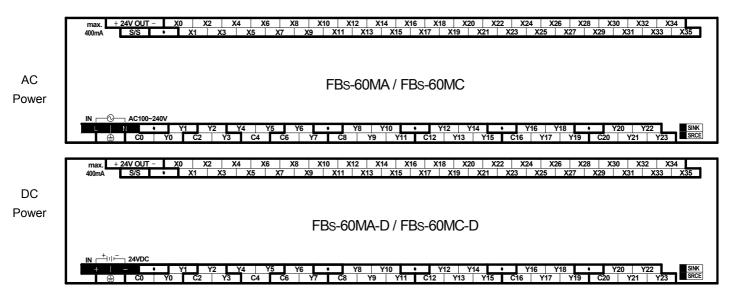

| 1.7.1 NC Control Main Unit                                                | H1-9  |

| 1.7.2 Basic/Advanced Main Unit                                            | H1-10 |

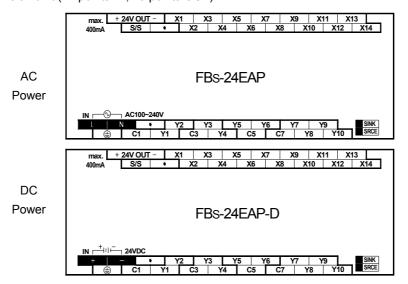

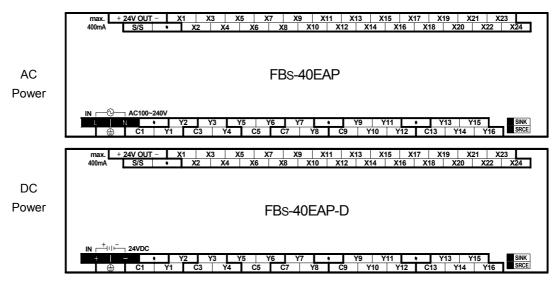

| 1.7.3 Digital I/O Expander                                                | H1-12 |

| 1.7.4 Digital I/O Expansion Module                                        | H1-13 |

| 1.7.5 High-Density Digital I/O Expansion Module                           | H1-14 |

| 1.7.6 Numeric I/O Expansion Module                                        | H1-14 |

| 1.7.7 Analog I/O Expansion Module                                         | H1-14 |

| 1.7.8 Temperature Input Module                                            | H1-15 |

| 1.7.9 Expansion Power                                                     | H1-15 |

| 1.7.10 Communication Module (CM)                                          | H1-16 |

| 1.7.11 Communication Board (CB)                                           | H1-17 |

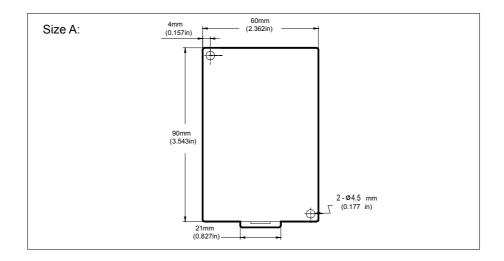

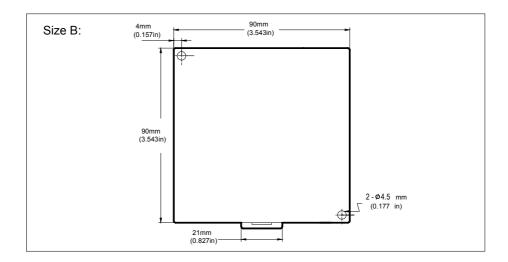

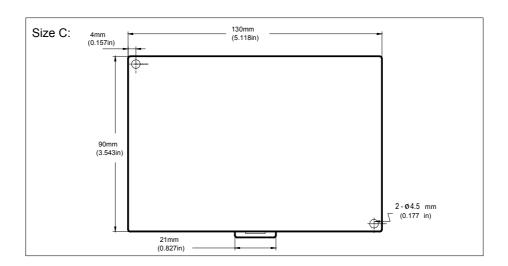

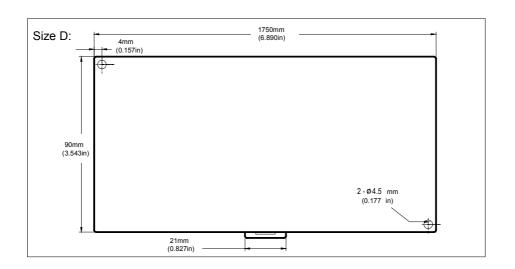

| 1.8 Drawings with External Dimensions                                     | H1-18 |

| Chapter 2 : System Architecture                                           |       |

| 2.1 Single-Unit System of FBS-PLC                                         | H2-1  |

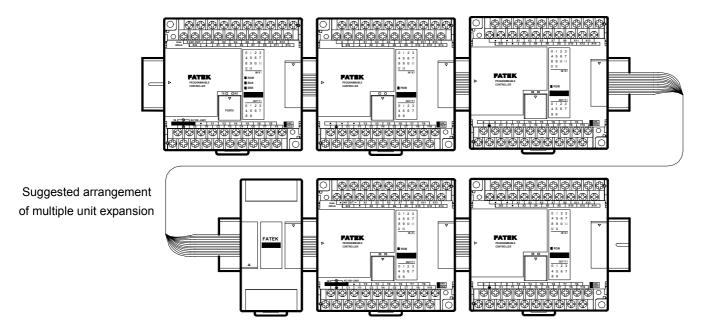

| 2.2 Formation of Multiple Units                                           | H2-2  |

| 2.2.1 Connection of multiple FBS-PLC                                      | H2-2  |

| 2.2.2 Connection of FBS-PLC with host computer or intelligent peripherals | H2-3  |

| Chapter 3:Expansion of FBS-PLC                                            |       |

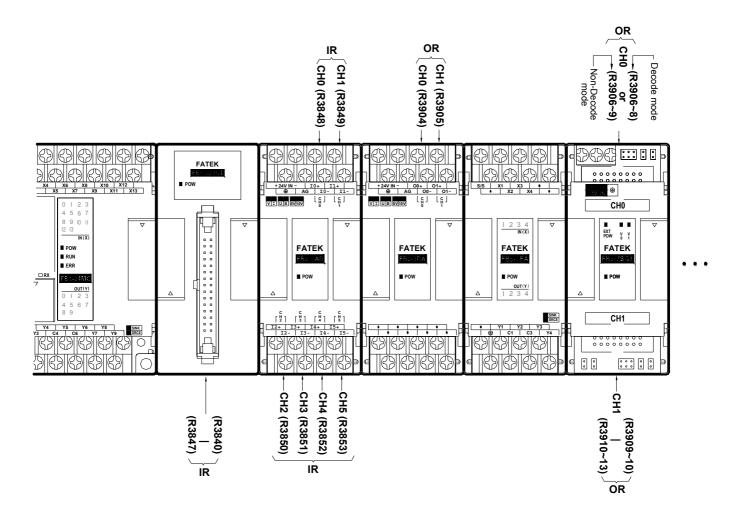

| 3.1 I/O Expansion                                                         | H3-1  |

|                                                                           |       |

| 3.1.1 Digital I/O Expansion and I/O Numbering                                      | H3-1                                 |

|------------------------------------------------------------------------------------|--------------------------------------|

| 3.1.2 Numeric I/O Expansion and I/O Channel Mapping                                | H3-3                                 |

| 3.2 Expansion of Communication Port                                                | H3-4                                 |

|                                                                                    |                                      |

| Chapter 4: Installation Guide                                                      |                                      |

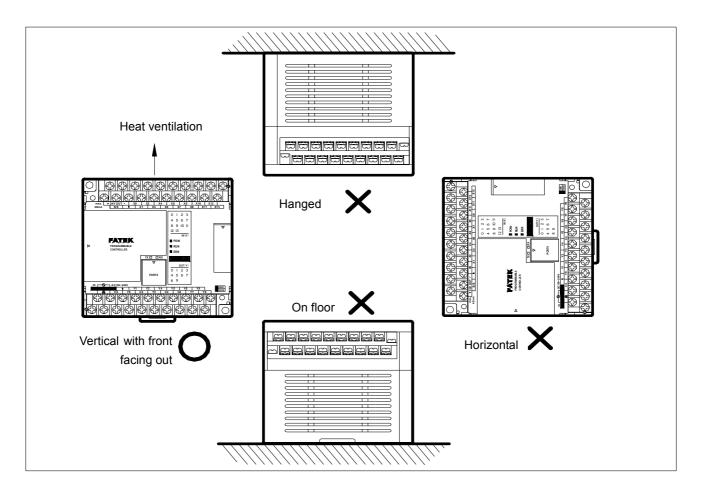

| 4.1 Installation Environment                                                       | H4-1                                 |

| 4.2 PLC Installation Precautions                                                   | H4-1                                 |

| 4.2.1 Placement of PLC                                                             | H4-1                                 |

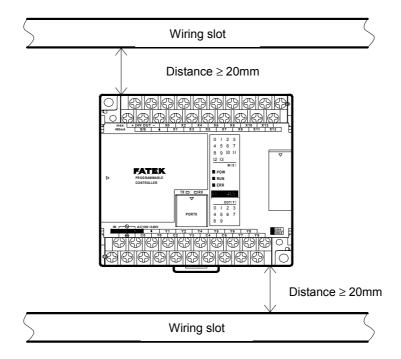

| 4.2.2 Ventilation Space                                                            | H4-2                                 |

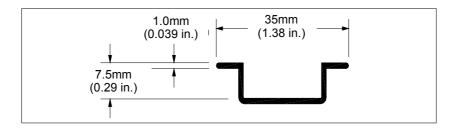

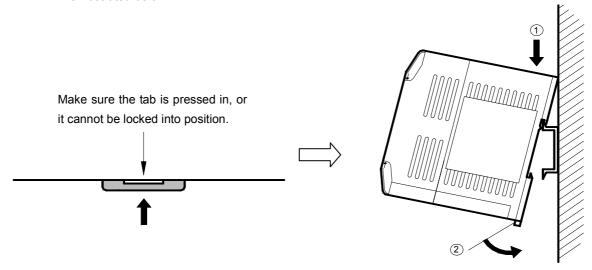

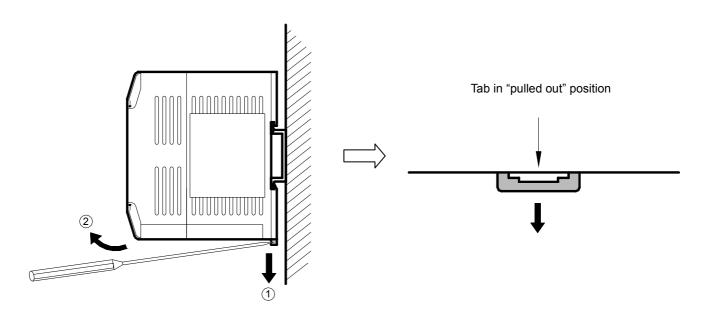

| 4.3 Fixation by DIN RAIL                                                           | H4-3                                 |

| 4.4 Fixation by Screws                                                             | H4-4                                 |

| 4.5 Precautions on Construction and Wiring                                         | H4-6                                 |

| Chapter 5: Wiring of Power Supply, Power Consumption Calculation                   | on, and                              |

| Power Sequence Requirement                                                         |                                      |

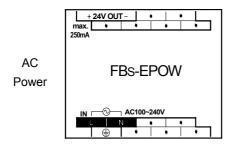

| 5.1 Specifications and Wiring of AC Power Sourced Power Supply                     | H5-1                                 |

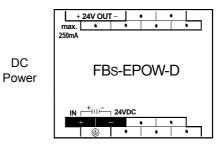

| 5.2 Specifications and Wiring of DC Power Sourced Power Supply                     | H5-2                                 |

|                                                                                    |                                      |

| 5.3 Residual Capacity of Main/Expansion Units and Current Consumption of Expansion | n Module                             |

| 5.3 Residual Capacity of Main/Expansion Units and Current Consumption of Expansio  |                                      |

|                                                                                    | H5-4                                 |

|                                                                                    | H5-4<br>H5-4                         |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4<br>H5-4<br>H5-5                 |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4<br>H5-4<br>H5-5                 |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4<br>H5-4<br>H5-5<br>H5-6         |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4<br>H5-4<br>H5-5<br>H5-6         |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4H5-4H5-5H5-6                     |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4H5-4H5-5H5-6                     |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4H5-4H5-5H5-6H6-1H6-2H6-3         |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4H5-4H5-5H5-6H6-1H6-2H6-3         |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4H5-4H5-5H5-6H6-1H6-2H6-3         |

| 5.3.1 Residual Capacity of Main Unit/Expansion Unit                                | H5-4H5-4H5-5H5-6H6-1H6-2H6-3H7-1H7-3 |

| 7.    | .3.3 Structure and Wiring of Single-End TRIAC Output Circuit                           | H7-5         |

|-------|----------------------------------------------------------------------------------------|--------------|

| 7.4   | Speed up the Single-End Transistor Output Circuit (only applicable to high and interme | diate-speed) |

|       |                                                                                        | H7-6         |

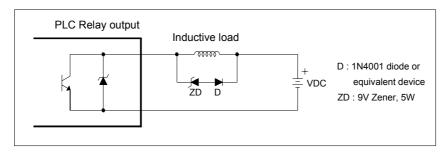

| 7.5   | Output Device Protection and Noise Suppression                                         | H7-6         |

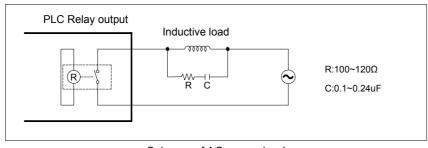

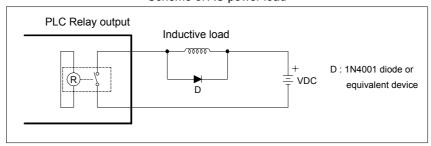

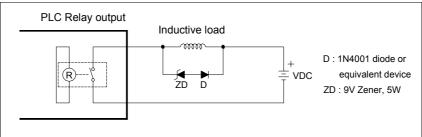

| 7.    | .5.1 Protection of Relay Contact and Noise Suppression                                 | H7-6         |

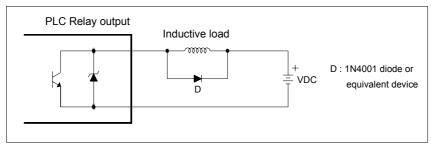

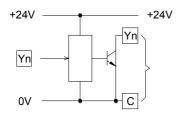

| 7.    | .5.2 Protection of Transistor and Noise Suppression                                    | H7-8         |

| Chapt | er 8 : Test Run, Monitoring and Maintenance                                            |              |

| 8.1   | Inspection after Wiring and before First Time Power on                                 | H8-1         |

| 8.2   | Test Run and Monitoring                                                                | H8-1         |

| 8.3   | LED Indications of Main Units and Troubleshooting                                      | H8-2         |

| 8.4   | Maintenance                                                                            | H8-4         |

| 8.5   | The charge of battery & recycle of used battery                                        | H8-4         |

# [Instruction]

# **Contents**

| Cha | apte  | er 1: PLC Ladder Diagram and the Coding Rules of Mnemonic     | )    |

|-----|-------|---------------------------------------------------------------|------|

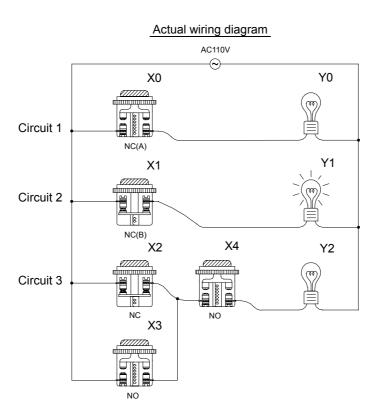

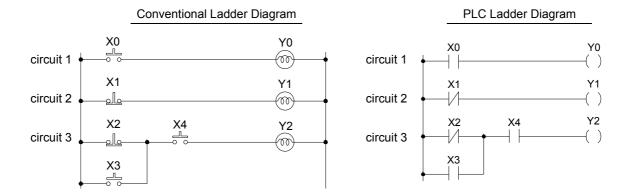

|     | 1.1   | The Operation Principle of Ladder Diagram                     | 1-1  |

|     | 1.1   | .1 Combination Logic ······ 1                                 | 1-1  |

|     | 1.1   | .2 Sequential Logic ······ 1                                  | 1-2  |

|     | 1.2   | Differences Between the Conventional and PLC Ladder Diagram 1 | 1-3  |

|     | 1.3   | Ladder Diagram Structure and Terminology 1                    | 1-5  |

|     | 1.4   | The Coding Rules of Mnemonic 1                                | 1-8  |

|     | 1.5 7 | The De-Composition of a Network ······· 1                     | 1-11 |

|     | 1.6   | Using Temporary Relays ······                                 | 1-12 |

|     | 1.7   | Program Simplification Techniques1                            | 1-13 |

| Cha | apte  | er 2: FBS-PLC Memory Allocation                               |      |

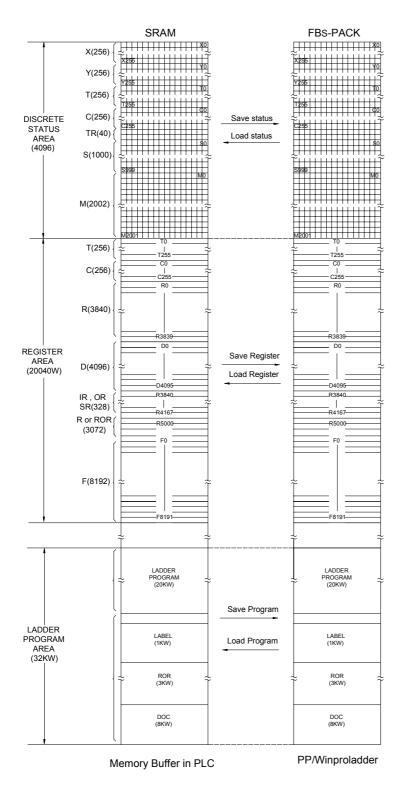

|     | 2.1   | FBs-PLC Memory Allocation 2                                   | 2-1  |

|     | 2.2   | Digital and Register Allocations                              | 2-2  |

|     | 2.3   | Special Relay Details                                         | 2-3  |

|     | 2.4   | Special Registers Details                                     | 2-8  |

| Cha | apte  | er 3: FBS-PLC Instruction Lists                               |      |

|     | 3.1   | Sequential Instructions                                       | 3-1  |

|     | 3.2   | Function Instructions ······ 3                                | 3-2  |

| Cha | apte  | er 4: Sequential Instructions                                 |      |

|     | 4.1   | Valid range of the Operand of Sequential Instructions         | 1-1  |

|     | 4.2   | Element Description ······                                    | 1-2  |

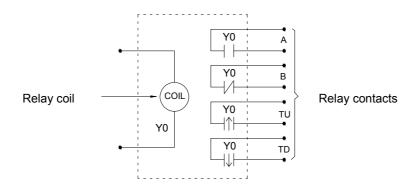

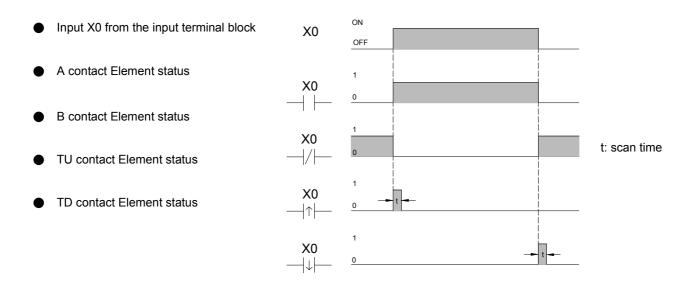

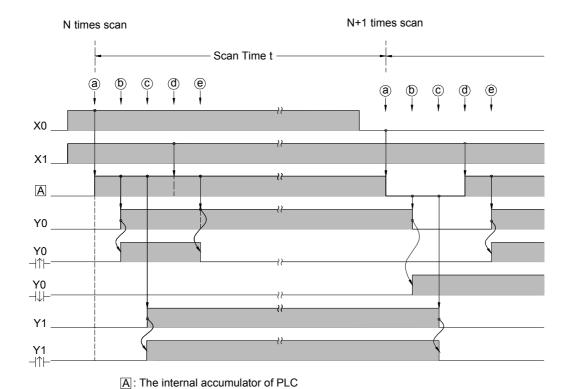

|     | 4.2   | .1 Characteristics of A, B, TU and TD Contacts ·······        | 1-2  |

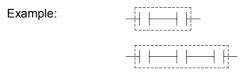

|     | 4.2   | .2 OPEN and SHORT Contact······4                              | 1-3  |

|     | 4.2   | .3 Output Coil and Inverse Output Coil······4                 | 1-4  |

|     | 4.2   | .4 Retentive Output Coil ······ 4                             | 1-4  |

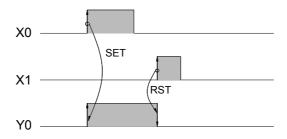

|     | 4.2   | .5 Set Coil and Reset Coil ······                             | 1-5  |

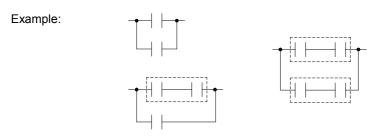

|     | 4.3   | Node Operation Instructions                                   | 1-5  |

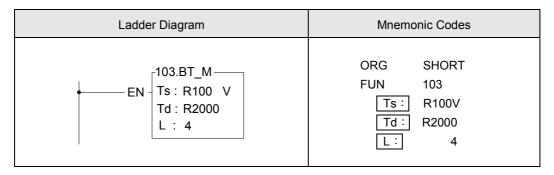

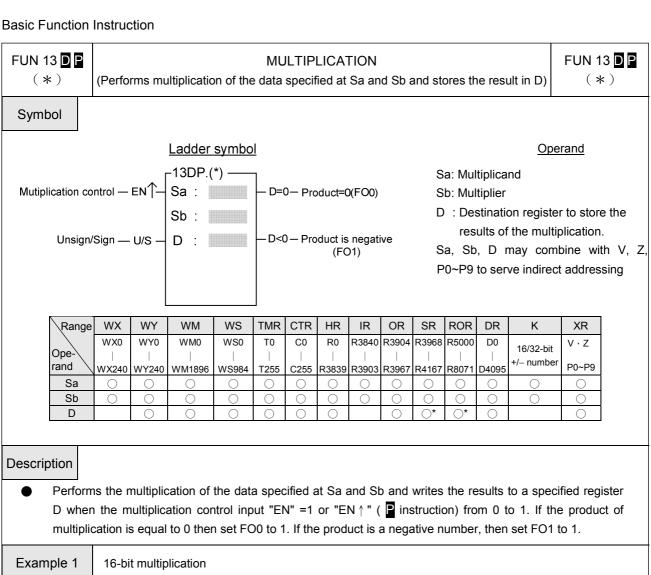

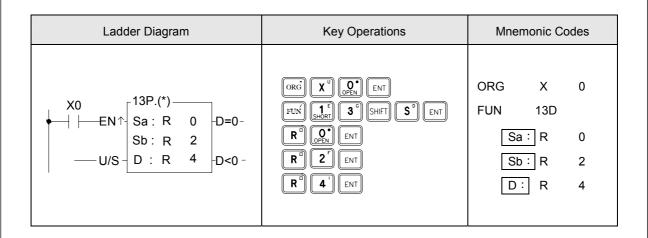

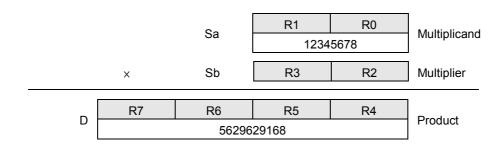

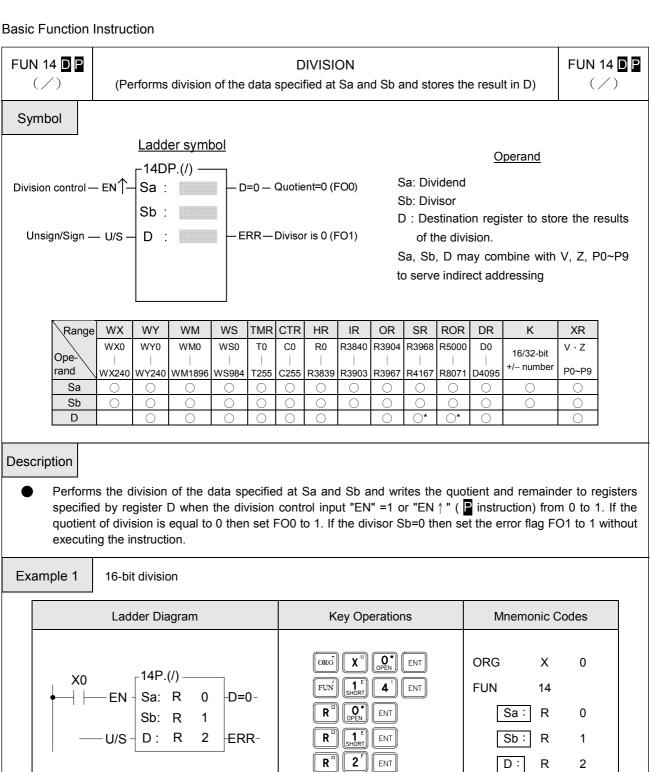

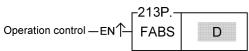

## Chapter 5: Description of Function Instructions

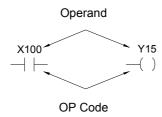

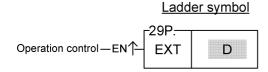

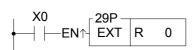

| 5.1  | The Format of Function Instructions.                                                                                                                                          |                                | 5-1                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------|

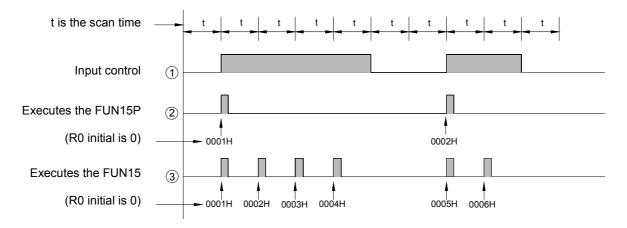

| 5    | .1.1 Input Control                                                                                                                                                            |                                | 5-1                                                                                                |

| 5    | .1.2 Instruction Number and Derivative In:                                                                                                                                    | structions                     | 5-2                                                                                                |

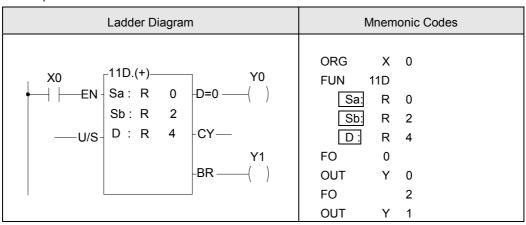

| 5    | .1.3 Operand                                                                                                                                                                  |                                | 5-3                                                                                                |

| 5    | .1.4 Functions Output (FO)                                                                                                                                                    |                                | 5-6                                                                                                |

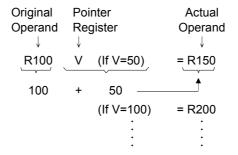

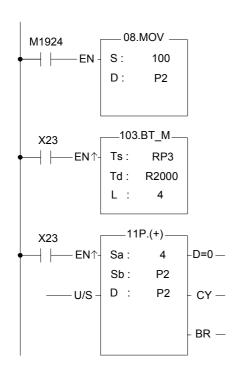

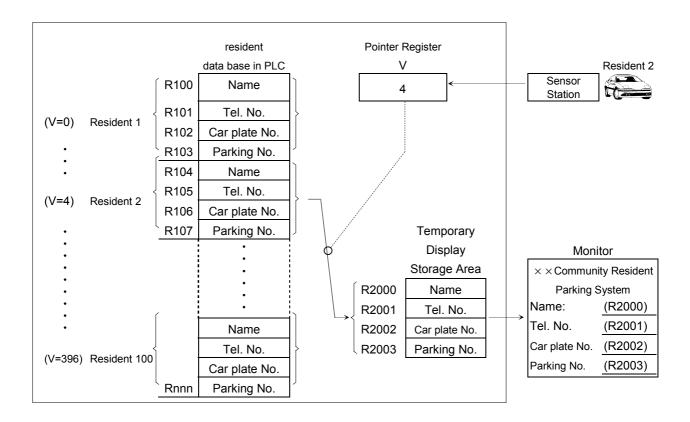

| 5.2  | Use Index Register(XR) for Indirect A                                                                                                                                         | Addressing                     | 5-6                                                                                                |

| 5.3  | Numbering System                                                                                                                                                              |                                | 5-9                                                                                                |

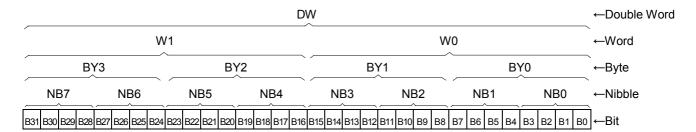

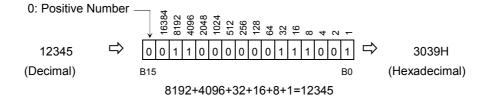

| 5    | .3.1 Binary Code and Relative Terminolog                                                                                                                                      | jies                           | 5-9                                                                                                |

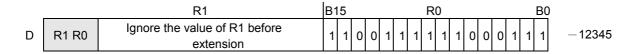

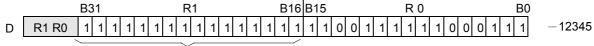

| 5    | .3.2 The Coding of Numeric Numbers for                                                                                                                                        | FBs-PLC                        | 5-11                                                                                               |

| 5    | .3.3 Range of Numeric Value                                                                                                                                                   |                                | 5-11                                                                                               |

| 5    | .3.4 Representation of Numeric Value                                                                                                                                          |                                | 5-11                                                                                               |

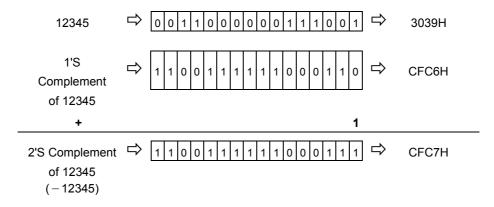

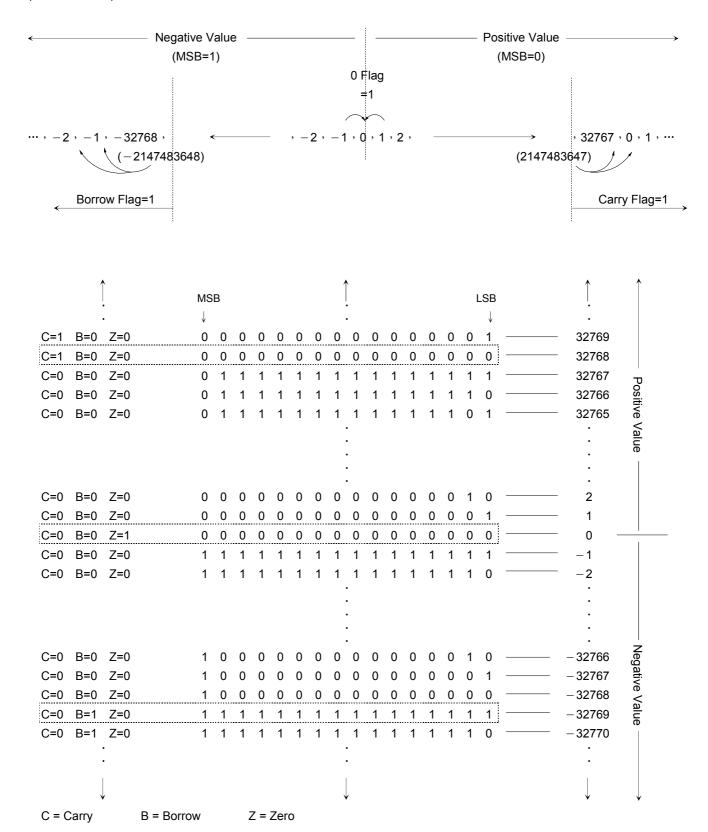

| 5    | .3.5 Representation of Negative Number.                                                                                                                                       |                                | 5-12                                                                                               |

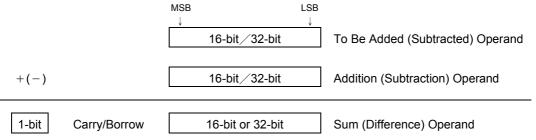

| 5.4  | Overflow and Underflow of Incremen                                                                                                                                            | t(+1) or Decrement(-1)         | 5-12                                                                                               |

| 5.5  |                                                                                                                                                                               | ction                          |                                                                                                    |

|      |                                                                                                                                                                               |                                |                                                                                                    |

| Chap | ter 6: Basic Function Instruct                                                                                                                                                | ions                           |                                                                                                    |

|      |                                                                                                                                                                               |                                |                                                                                                    |

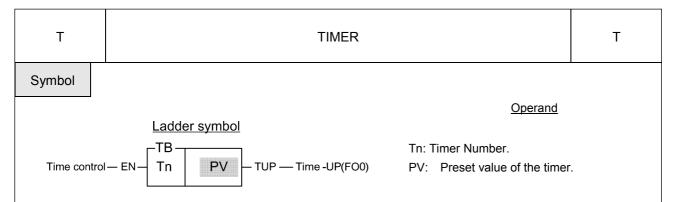

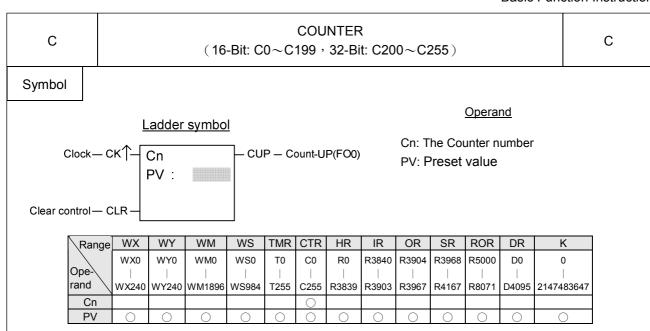

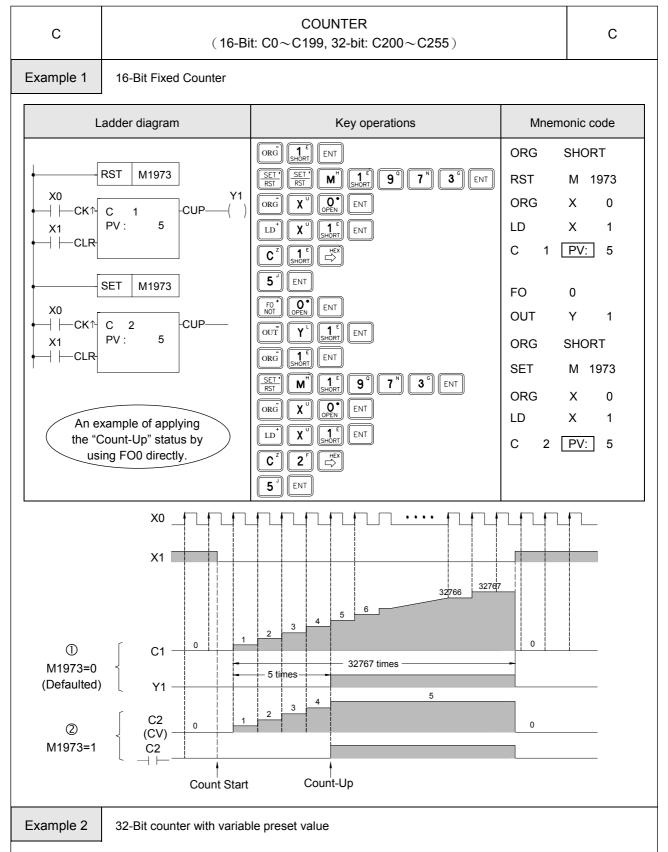

| •    | Т                                                                                                                                                                             | (Timer)                        | 6-2                                                                                                |

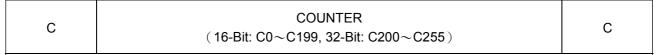

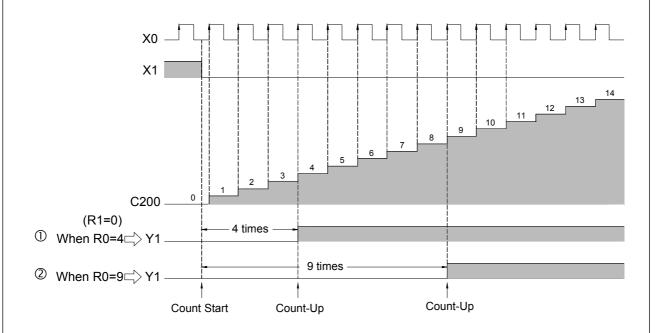

| •    | T<br>C                                                                                                                                                                        | (Timer)(Counter)               |                                                                                                    |

| •    |                                                                                                                                                                               |                                | 6-5                                                                                                |

| •    | С                                                                                                                                                                             | (Counter)                      | 6-5<br>6-8                                                                                         |

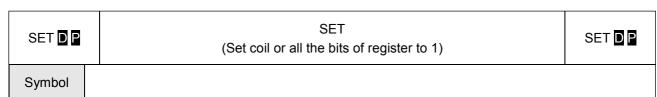

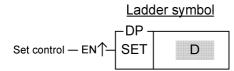

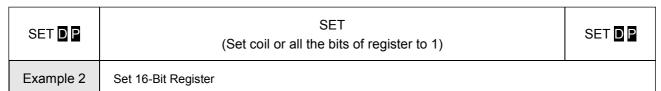

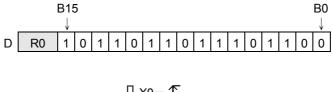

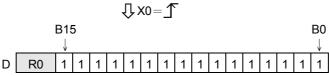

| •    | C<br>Set                                                                                                                                                                      | (Counter)(SET)                 | 6-5<br>6-8<br>6-10                                                                                 |

| •    | C<br>Set<br>Reset                                                                                                                                                             | (Counter)(SET) (RESET)         | 6-5<br>6-8<br>6-10<br>6-12                                                                         |

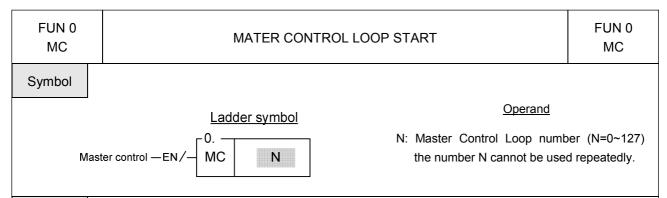

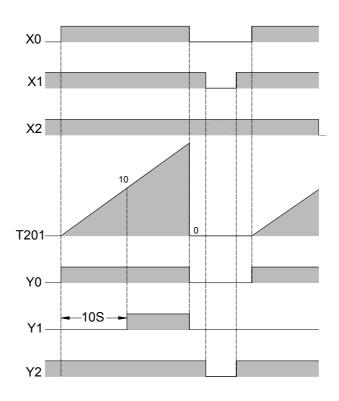

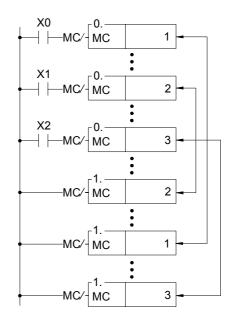

| •    | C Set Reset Master control loop start                                                                                                                                         | (Counter) (SET) (RESET) (FUN0) | 6-5<br>6-8<br>6-10<br>6-12<br>6-14                                                                 |

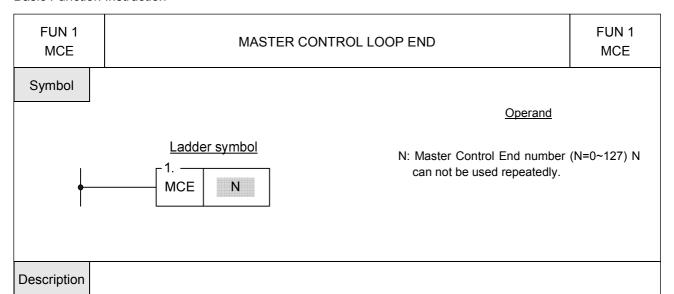

| •    | C Set Reset Master control loop start Master control loop end                                                                                                                 | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17                                                 |

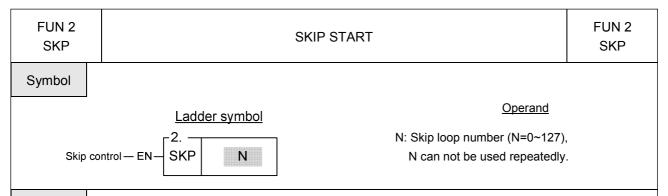

| •    | C Set Reset Master control loop start Master control loop end Skip start                                                                                                      | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17                                                 |

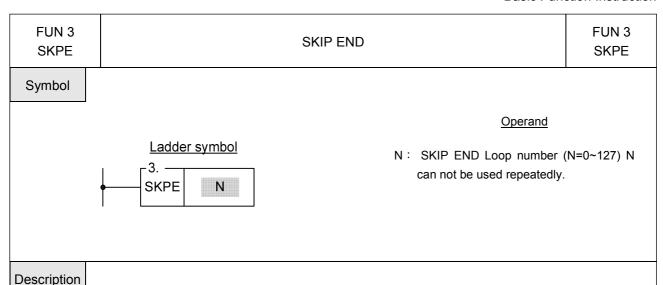

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end                                                                                             | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18                                         |

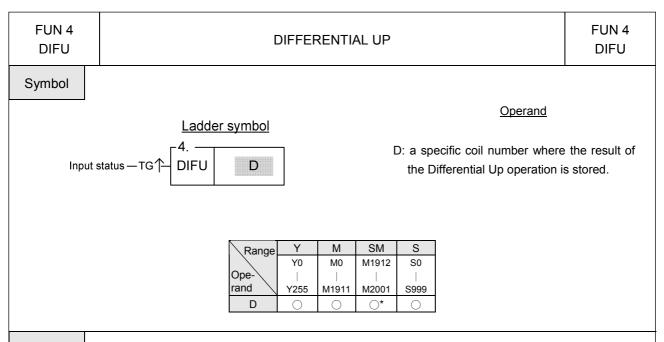

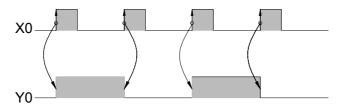

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up                                                                             | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18<br>6-19<br>6-20                         |

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up Differential down                                                           | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18<br>6-19<br>6-20                         |

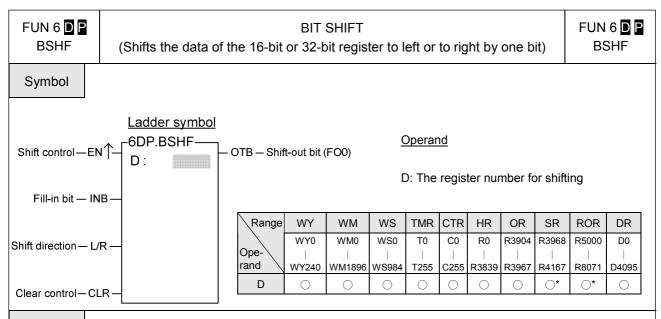

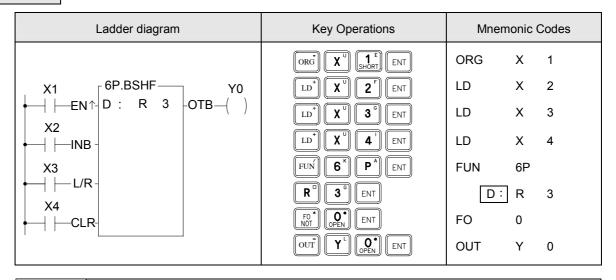

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up Differential down Bit shift                                                 | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18<br>6-19<br>6-20<br>6-21                 |

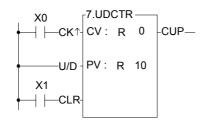

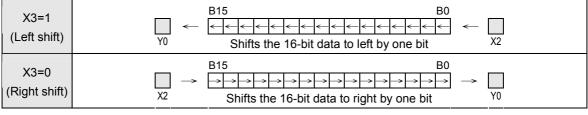

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up Differential down Bit shift Up/down counter                                 | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18<br>6-20<br>6-21<br>6-23                 |

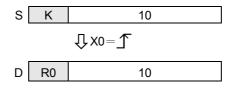

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up Differential down Bit shift Up/down counter Move                            | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18<br>6-20<br>6-21<br>6-23<br>6-24         |

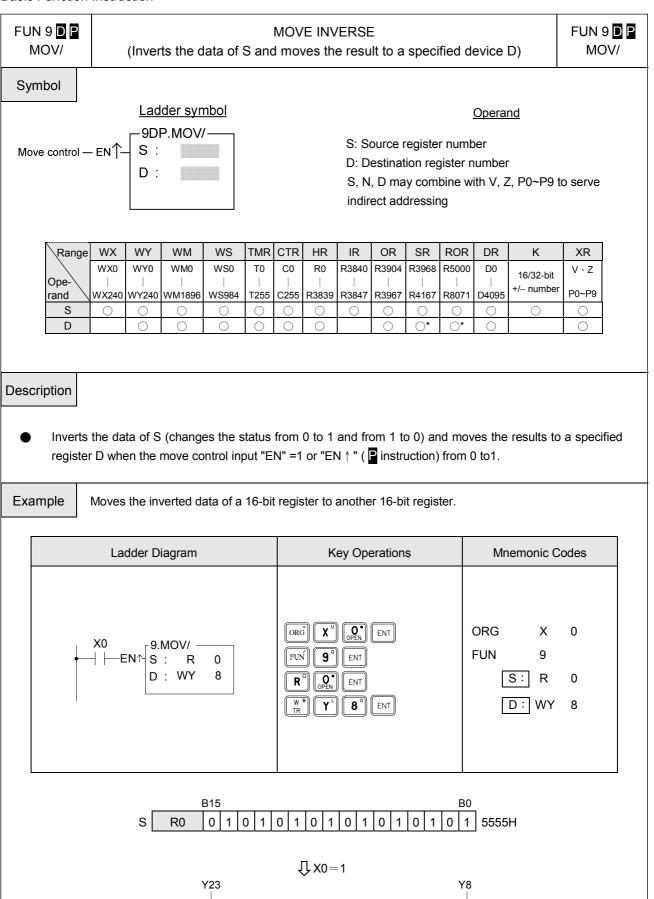

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up Differential down Bit shift Up/down counter Move Move inverse               | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-17<br>6-18<br>6-20<br>6-21<br>6-23<br>6-24<br>6-25 |

| •    | C Set Reset Master control loop start Master control loop end Skip start Skip end Differential up Differential down Bit shift Up/down counter Move Move inverse Toggle switch | (Counter)                      | 6-5<br>6-8<br>6-10<br>6-12<br>6-14<br>6-15<br>6-19<br>6-20<br>6-21<br>6-23<br>6-24<br>6-25<br>6-26 |

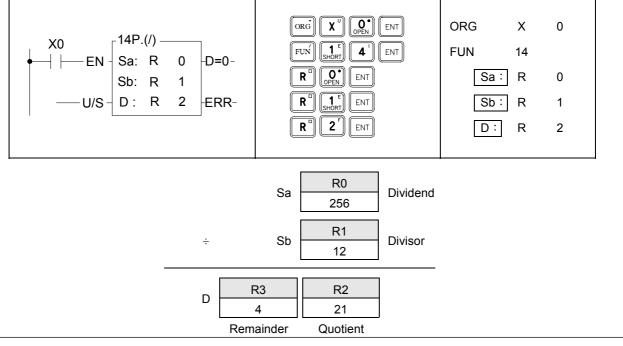

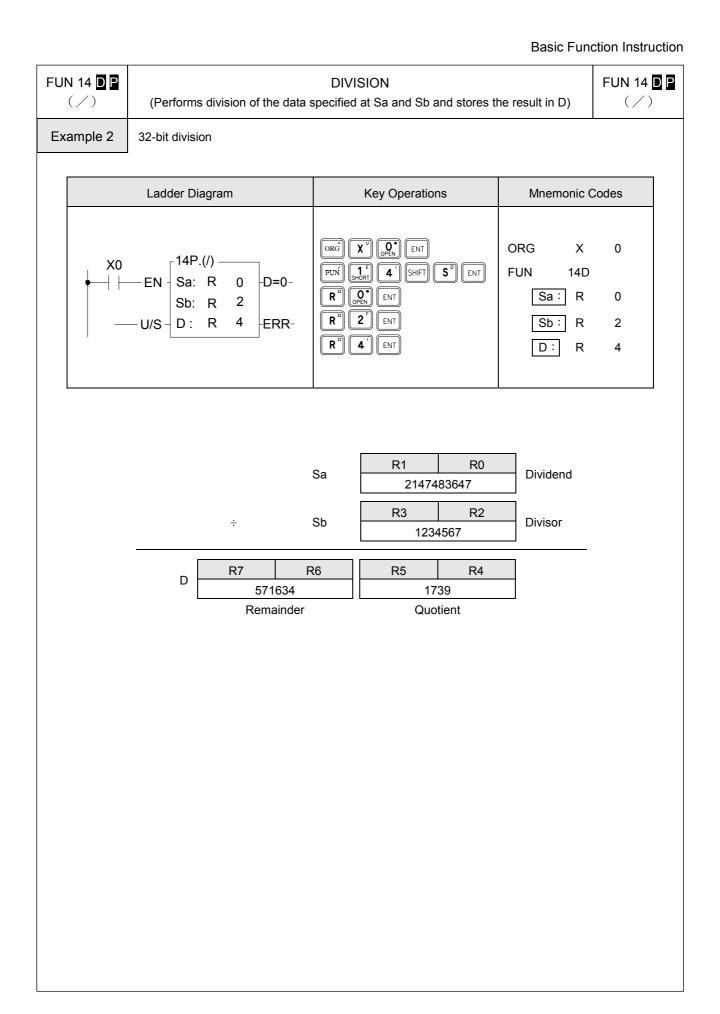

| •     | Division                                 | (FUN14)6-30                  |

|-------|------------------------------------------|------------------------------|

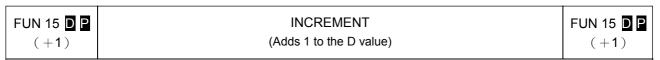

| •     | Increment                                | (FUN15)6-32                  |

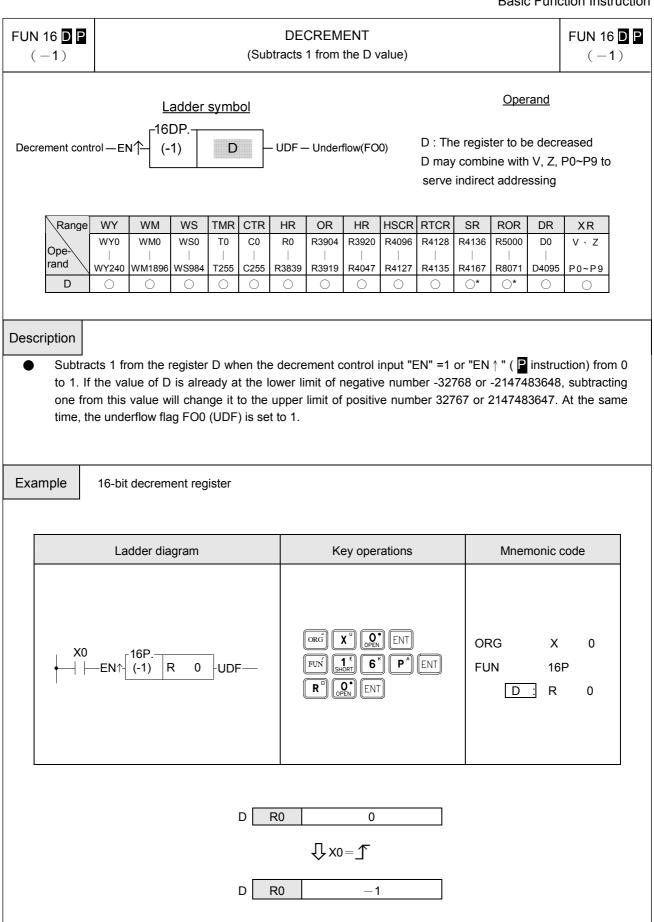

| •     | Decrement                                | (FUN16)6-33                  |

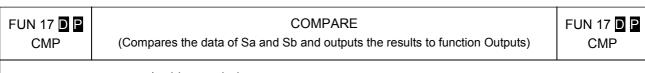

| •     | Compare                                  | (FUN17)6-34                  |

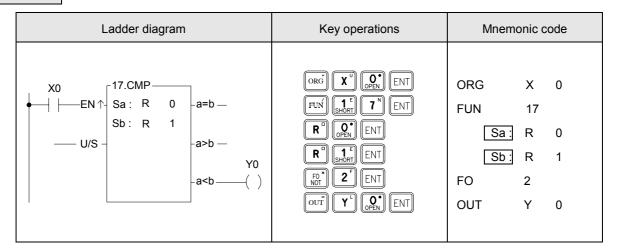

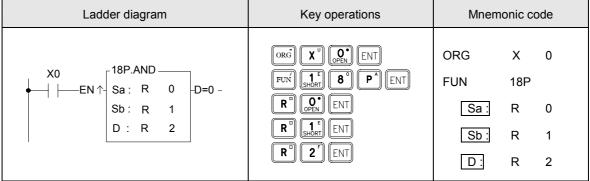

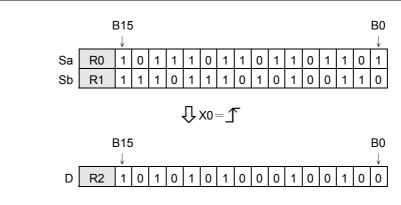

| •     | Logical and                              | (FUN18)6-35                  |

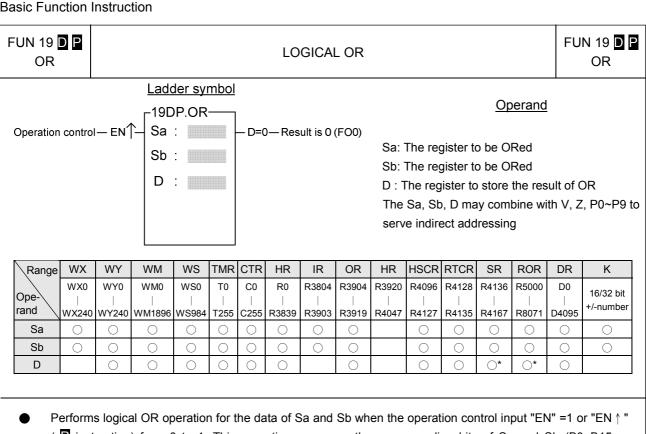

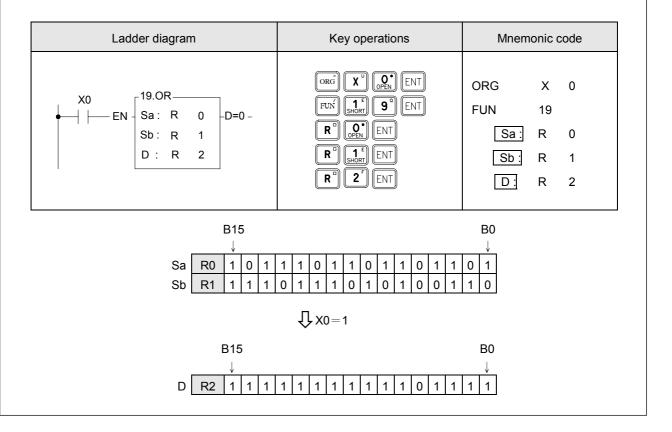

| •     | Logical or                               | (FUN19)6-36                  |

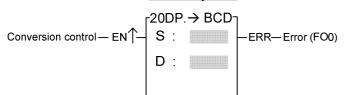

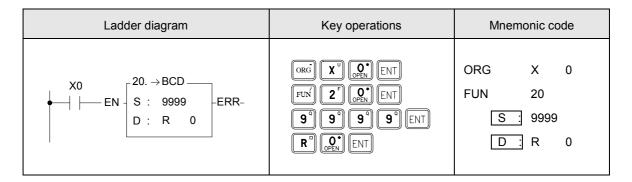

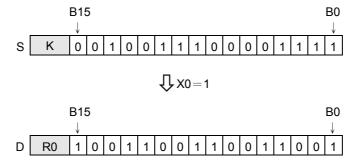

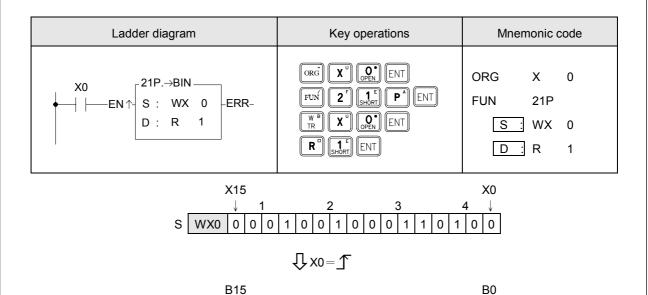

| •     | Binary to bcd conversion                 | (FUN20)6-37                  |

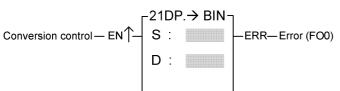

| •     | Bcd to binary conversion                 | (FUN21)6-38                  |

| Chapt | er 7:Advanced Function Insti             | ructions                     |

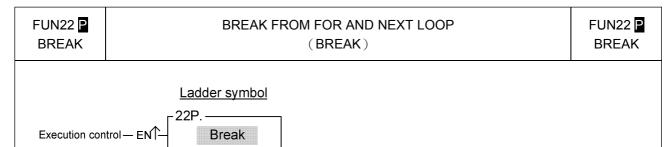

| •     | Flow control instructions1               | (FUN22)7-1                   |

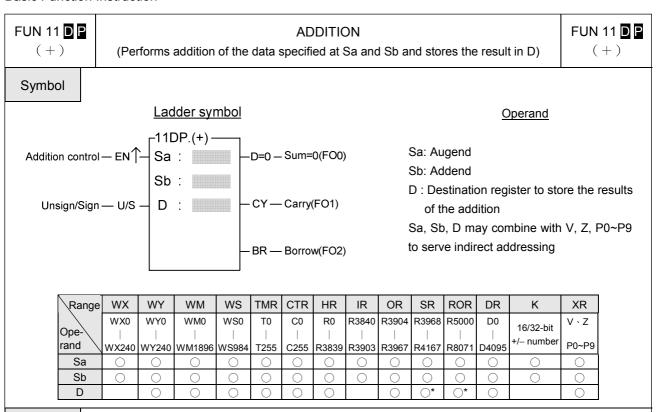

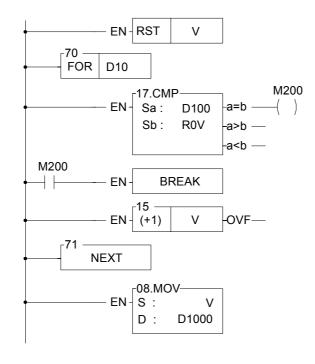

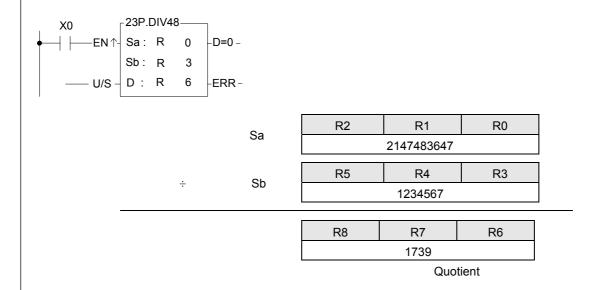

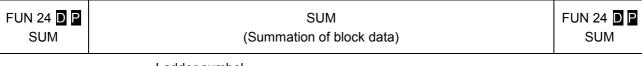

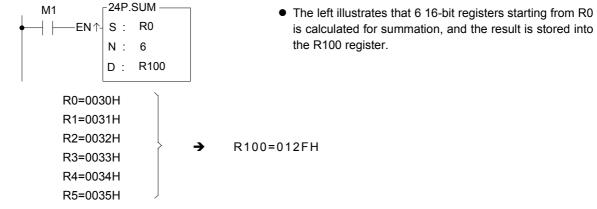

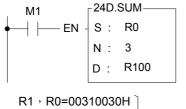

| •     | Arithmetical operation instructions      | (FUN23~32)7-2~7-9            |

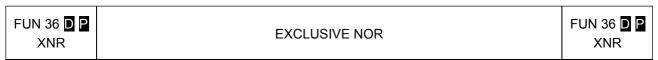

| •     | Logical operation instructions           | (FUN35~36)7-10~7-13          |

| •     | Comparison instruction                   | (FUN37)7-14                  |

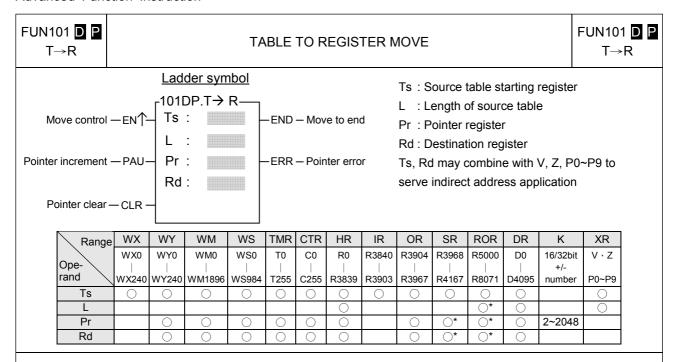

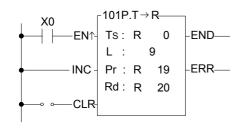

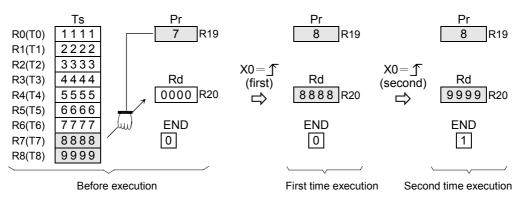

| •     | Data movement instructions1              | (FUN40~50)7-15~7-25          |

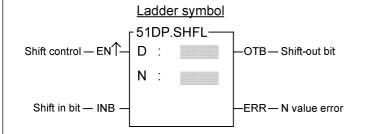

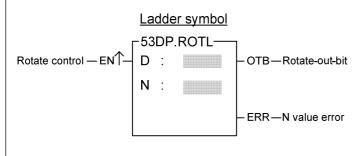

| •     | Shifting / Rotating instructions         | (FUN51~54)7-26~7-29          |

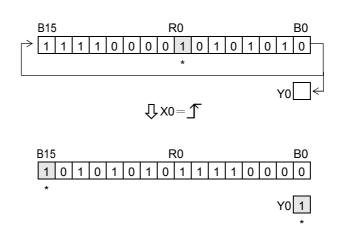

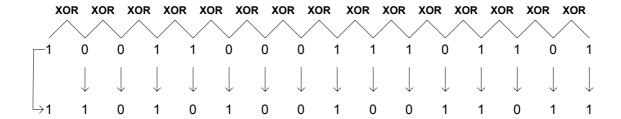

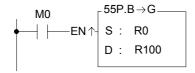

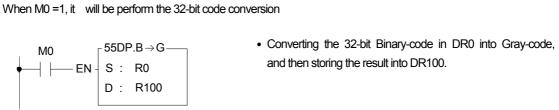

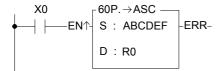

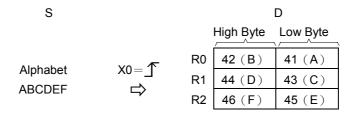

| •     | Code conversion instructions             | (FUN55~64)7-30~7-46          |

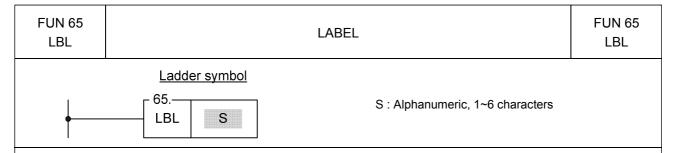

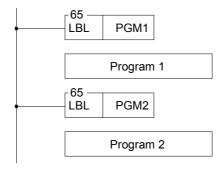

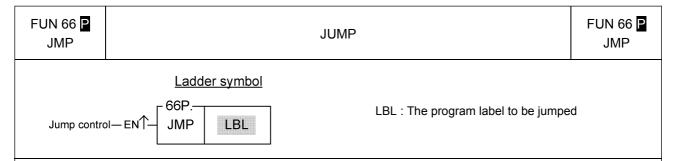

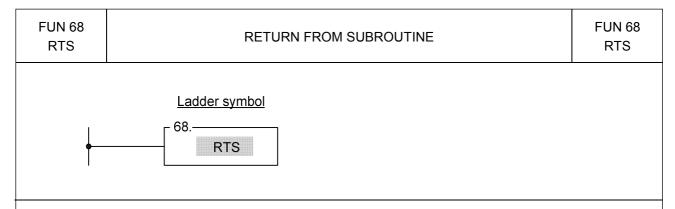

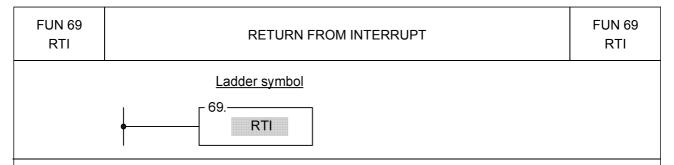

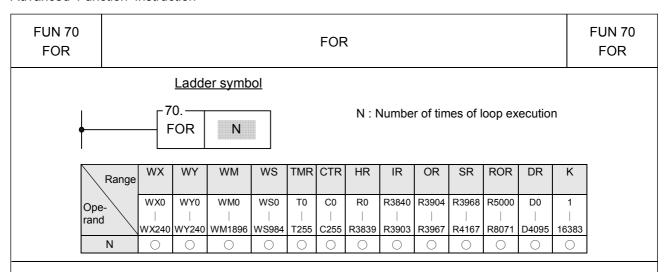

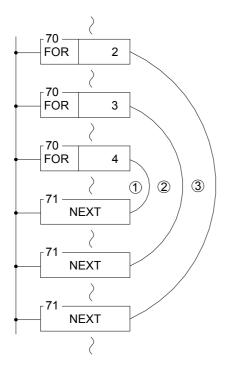

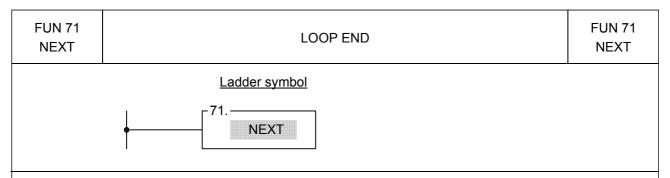

| •     | Flow control instructions2               | (FUN65~71)7-47~7-54          |

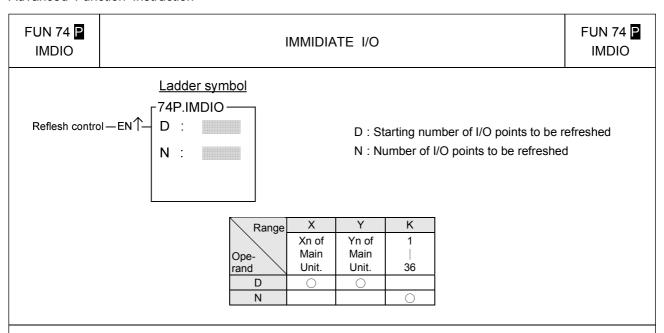

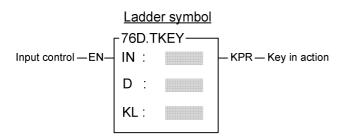

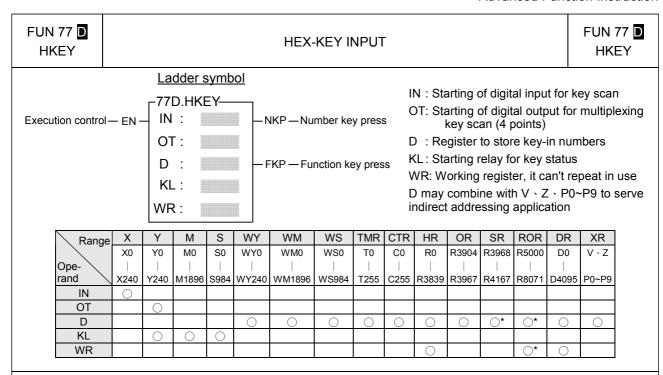

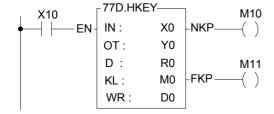

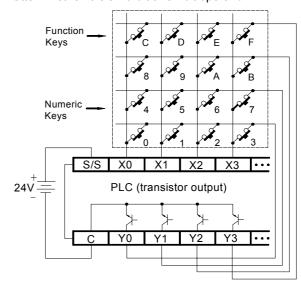

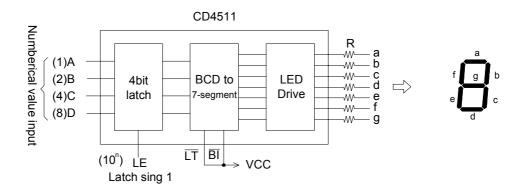

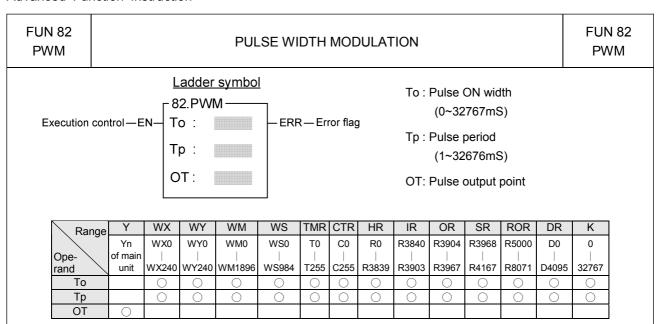

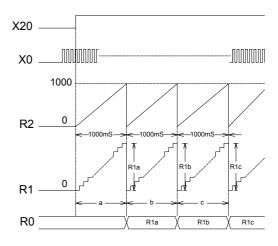

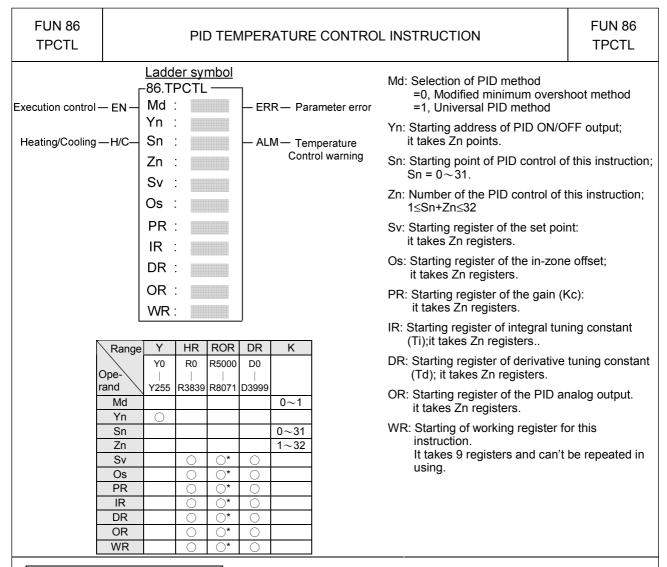

| •     | I/O instructions                         | (FUN74~86)7-55~7-72          |

| •     | Cumulative timer instructions            | (FUN87~89)7-73~7-74          |

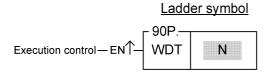

| •     | Watchdog timer instructions              | (FUN90~91)7-75~7-76          |

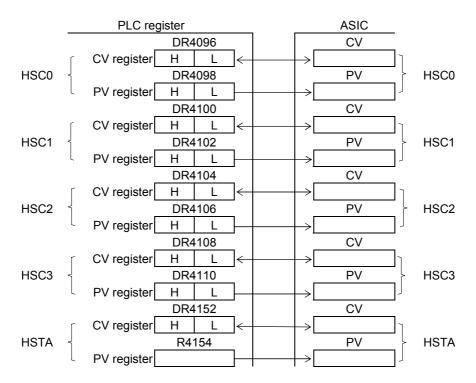

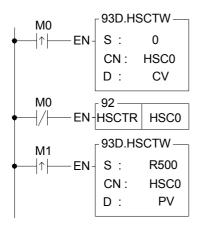

| •     | High speed counting / timing             | (FUN92~93)7-77~7-78          |

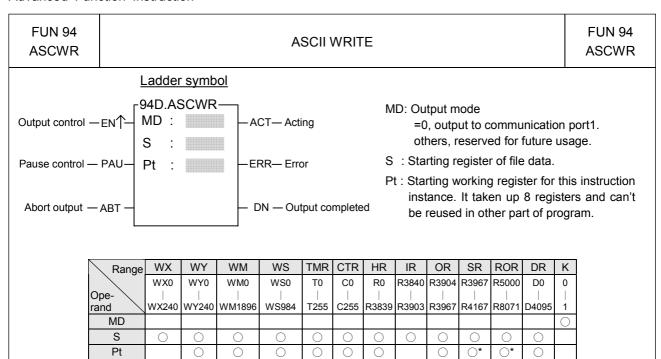

| •     | Report printing instructions             | (FUN94)7-79 ~ 7-80           |

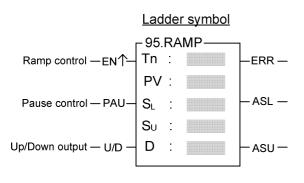

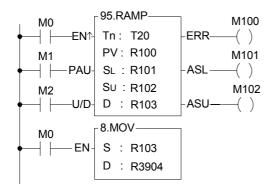

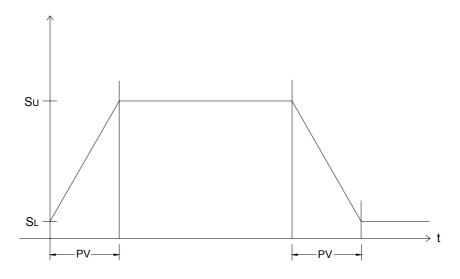

| •     | Slow up / Slow down instructions         | (FUN95)7-81 ~ 7-82           |

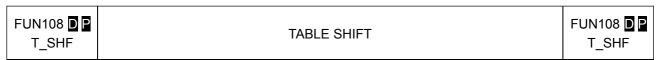

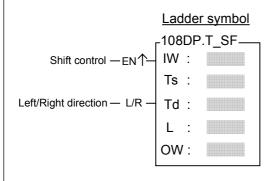

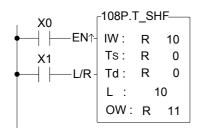

| •     | Table instructions                       | (FUN100~114)7-84~7-101       |

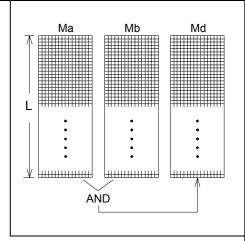

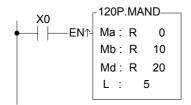

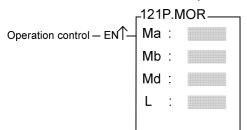

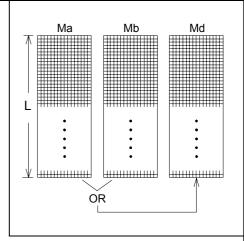

| •     | Matrix instructions                      | (FUN120~130)7-103 ~ 7-113    |

| •     | NC positioning instructions              | (FUN139~143)7-114 ~ 7-119    |

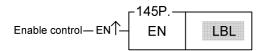

| •     | Enable / Disable instructions            | (FUN145~146)7-120~7-121      |

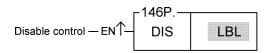

| •     | Communication instructions               | (FUN150~151)7-122~7-123      |

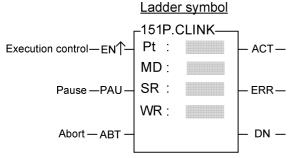

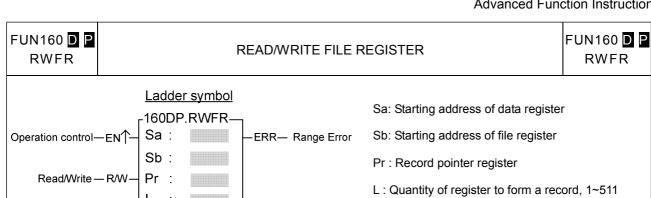

| •     | Data movement instructions2              | (FUN160)7-124 ~ 7-125        |

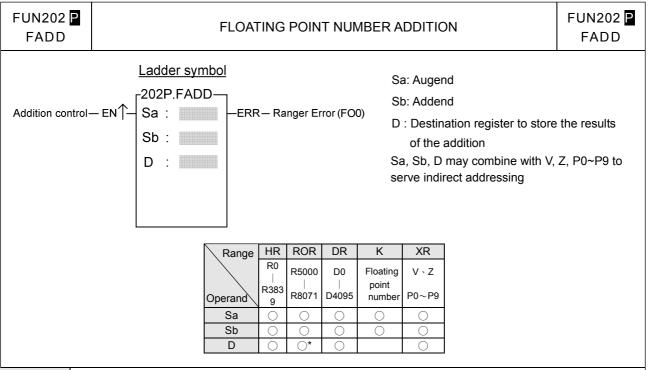

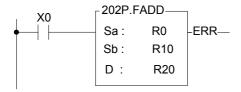

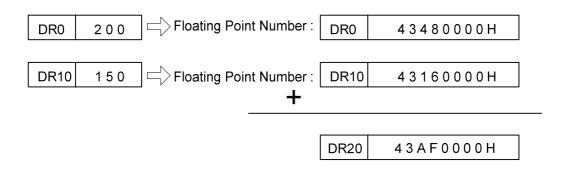

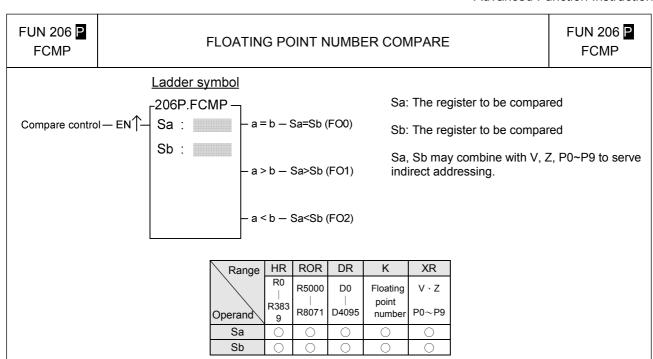

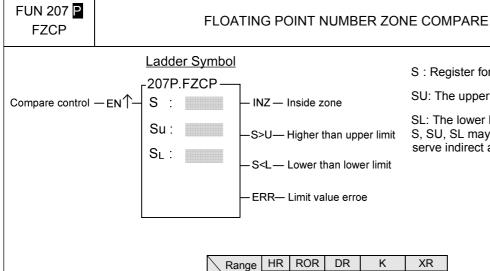

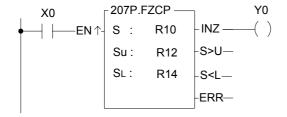

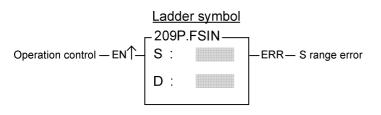

| •     | Floating Arithmetical operation instruct | tions(FUN200~213)7-126~7-140 |

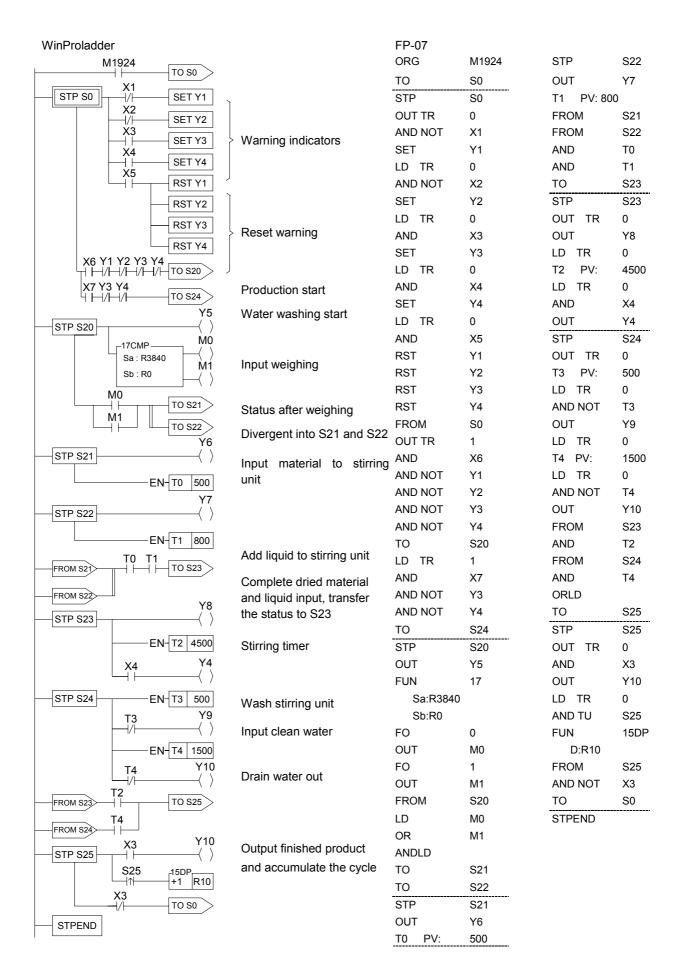

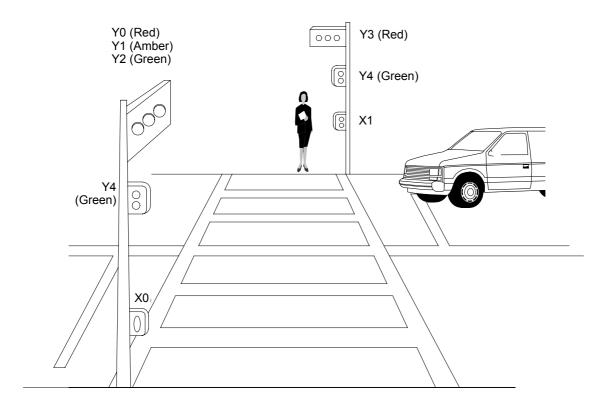

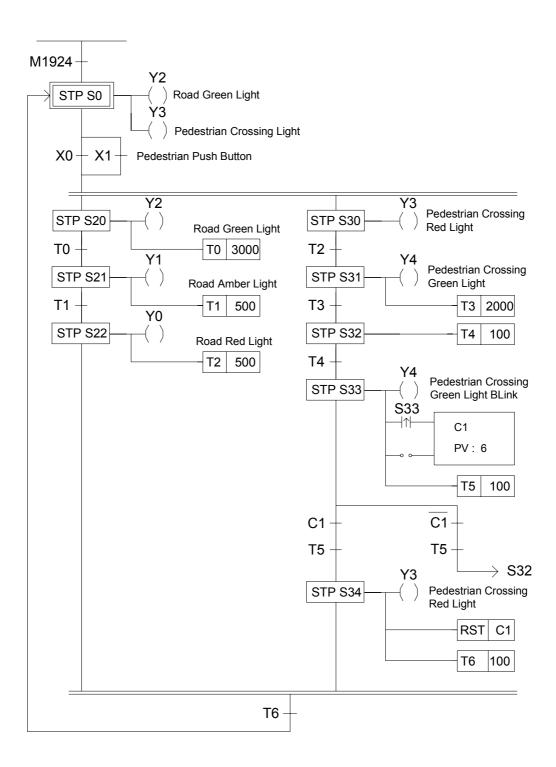

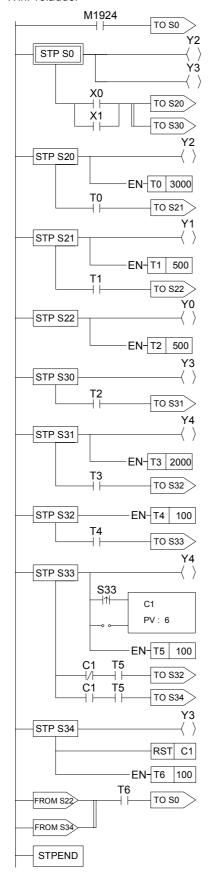

| Chapt | er 8: Step Instruction Descrip           | otion                        |

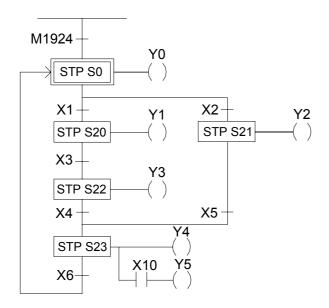

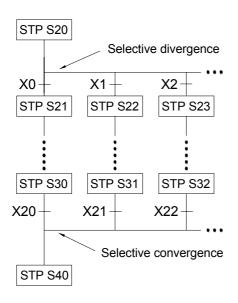

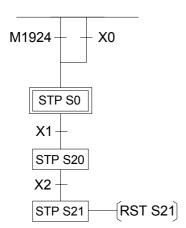

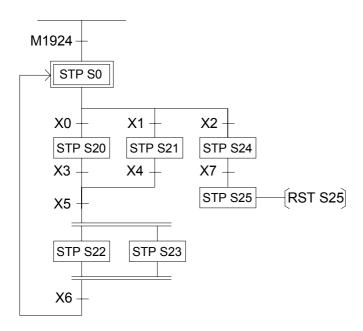

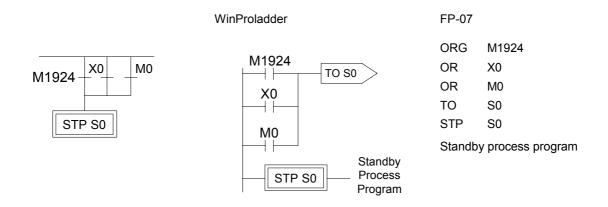

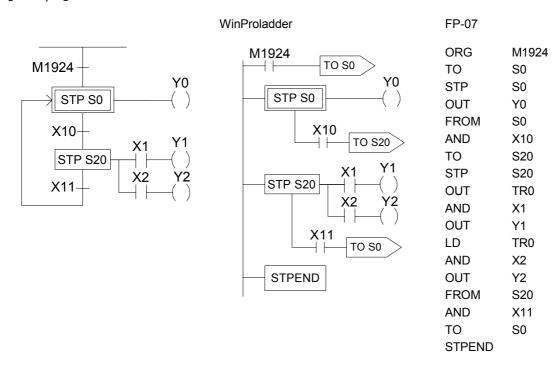

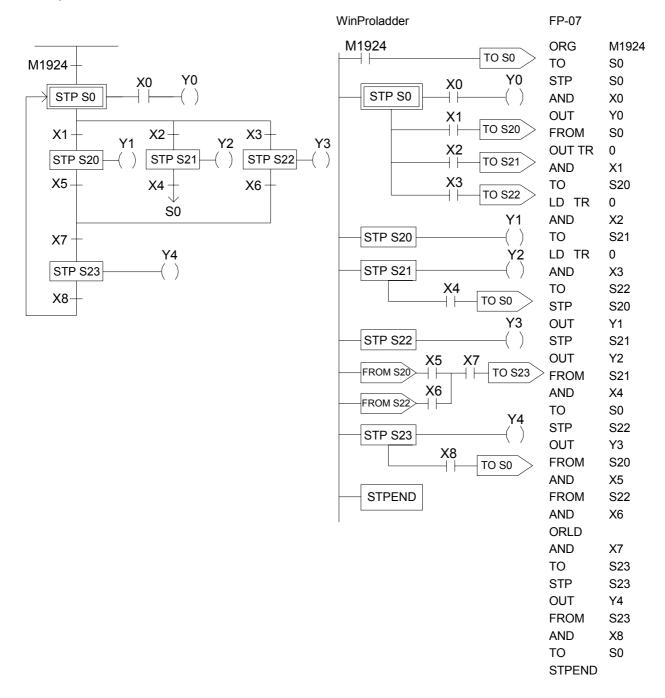

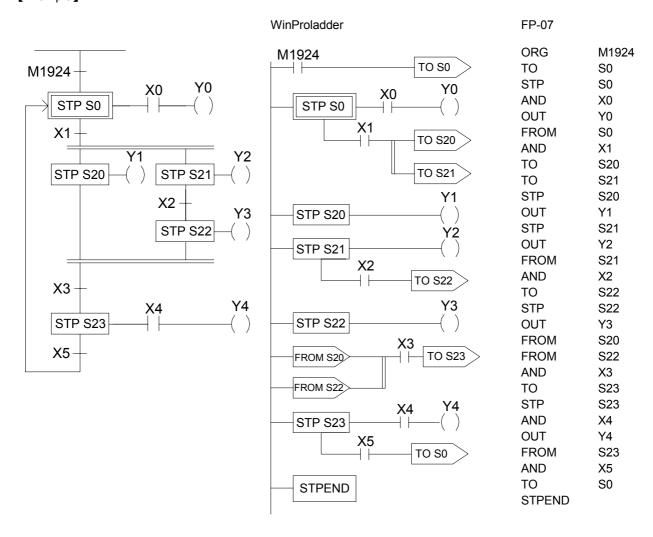

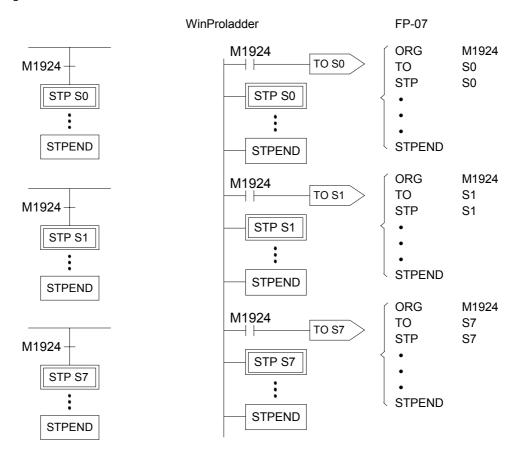

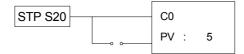

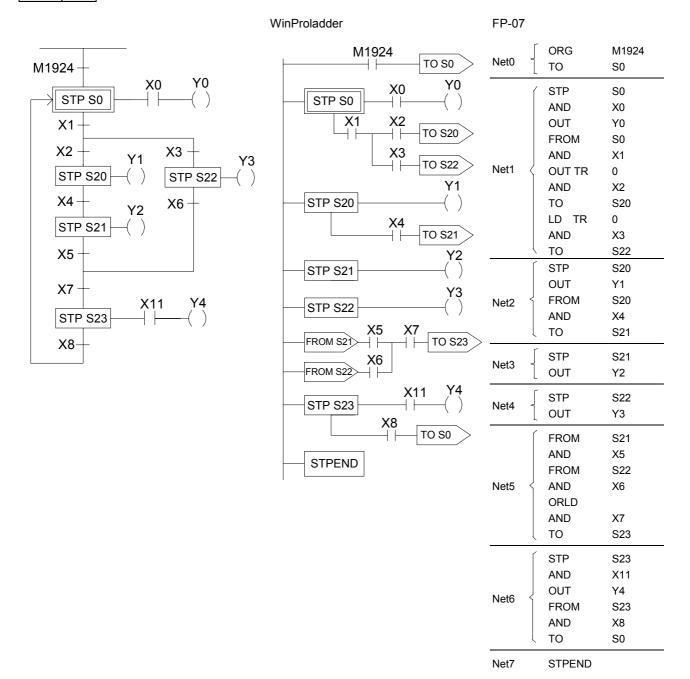

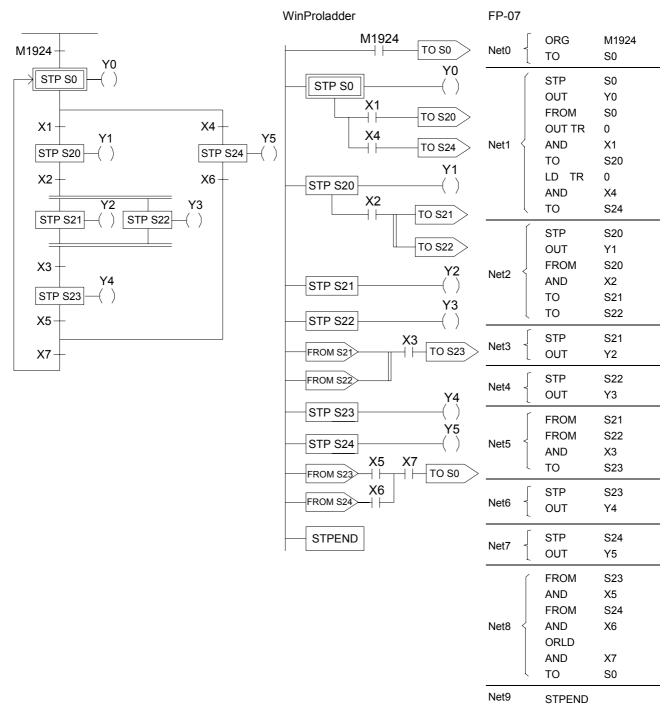

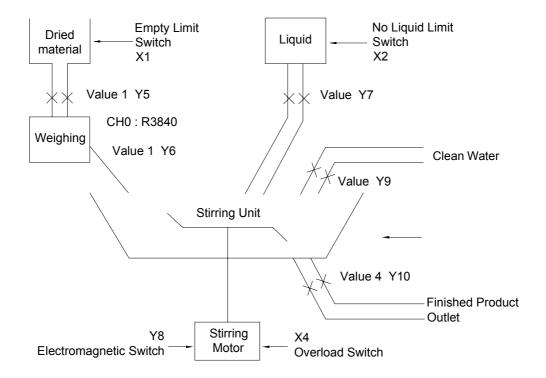

| 8.1   | The Operation Principle of Step Ladd     | er Diagram ····· 8-1         |

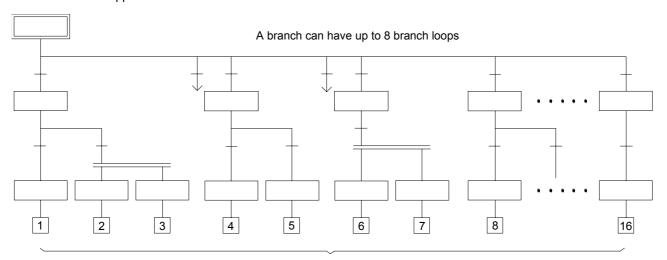

| 8.2   | Basic Formation of Step Ladder Diag      | ram 8-2                      |

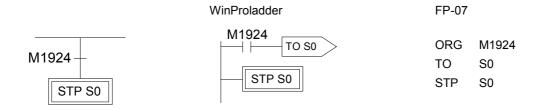

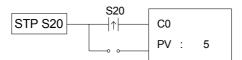

| 8.3   | Instruction of Step Introduction: STP,   | FROM, TO, and STPEND 8-5     |

| 8.4   | Notes for Writing a Step Ladder Diago    | ram 8-11                     |

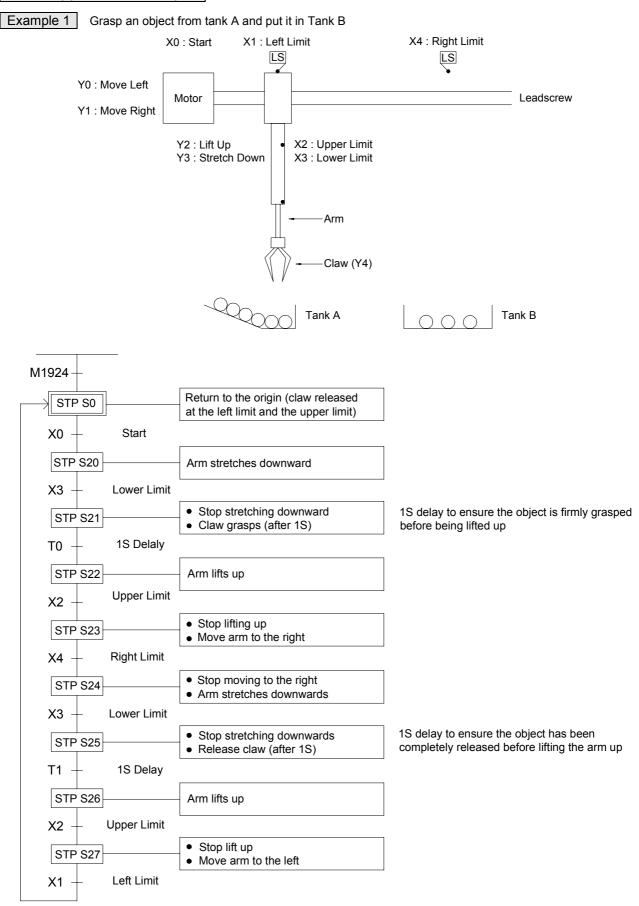

| 8.5  | Application Examples ······ 8-15                      |

|------|-------------------------------------------------------|

| 8.6  | Syntax Check Error Codes for Step Instruction8-22     |

|      |                                                       |

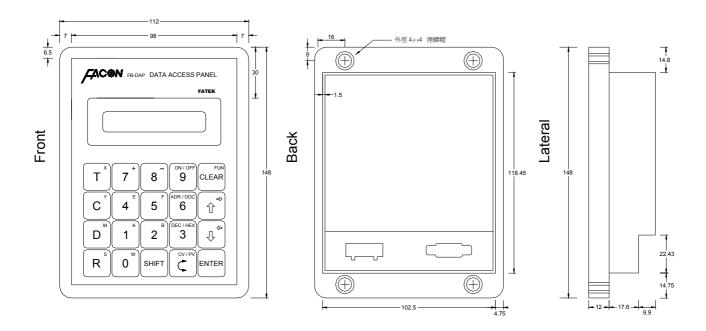

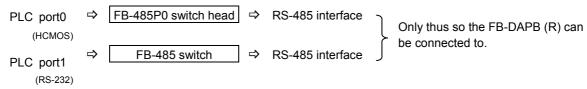

| [App | endix DAP Simple Human Machine Interface              |

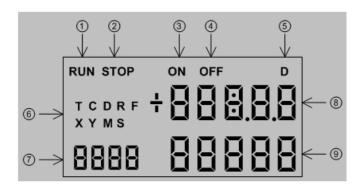

| 1.1  | Profile                                               |

| 1.2  | Important points before operation                     |

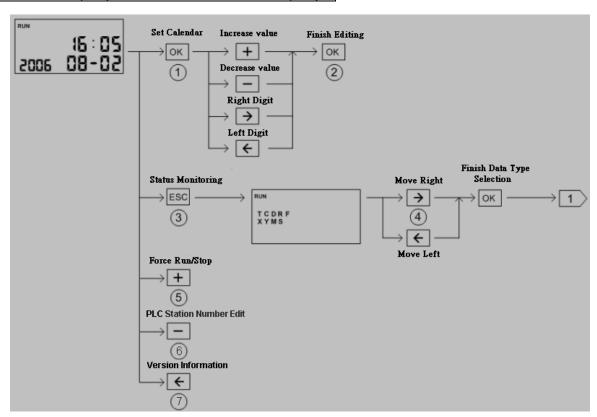

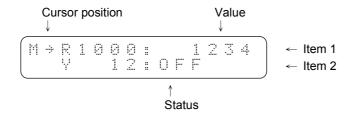

| 1.3  | The Main Functions of FBs-DAP                         |

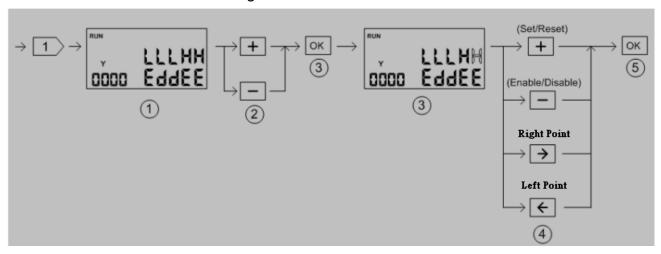

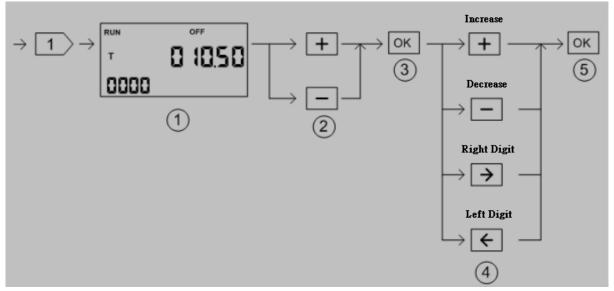

| 1.4  | Setter Functions of General Information               |

| 1.5  | FUN Functions                                         |

| 1.5  | 5.1 In and out of FUN functions····                   |

| 1.5  | 5.2 FUN function description                          |

| 1.6  | Wireless card reading functions                       |

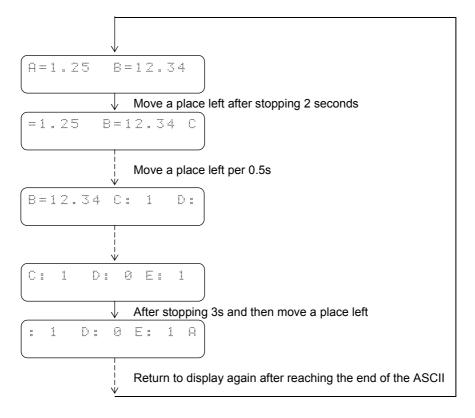

| 1.7  | Special message display function                      |

| 1.7  | 7.1 Message display application·····                  |

| 1.7  | 7.2 The Information formats of messages (ASCII Table) |

### [ Hardware ]

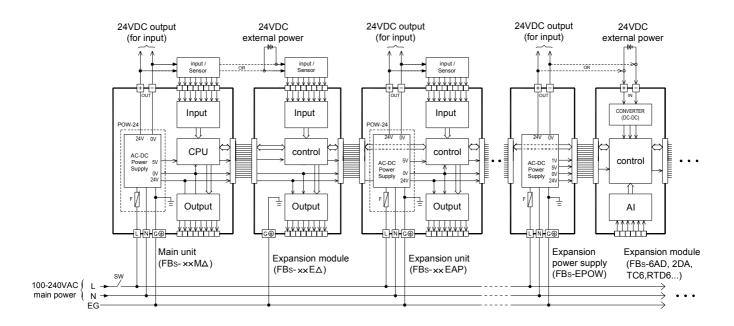

### **Chapter 1** Introduction of FATEK FBS Series PLC

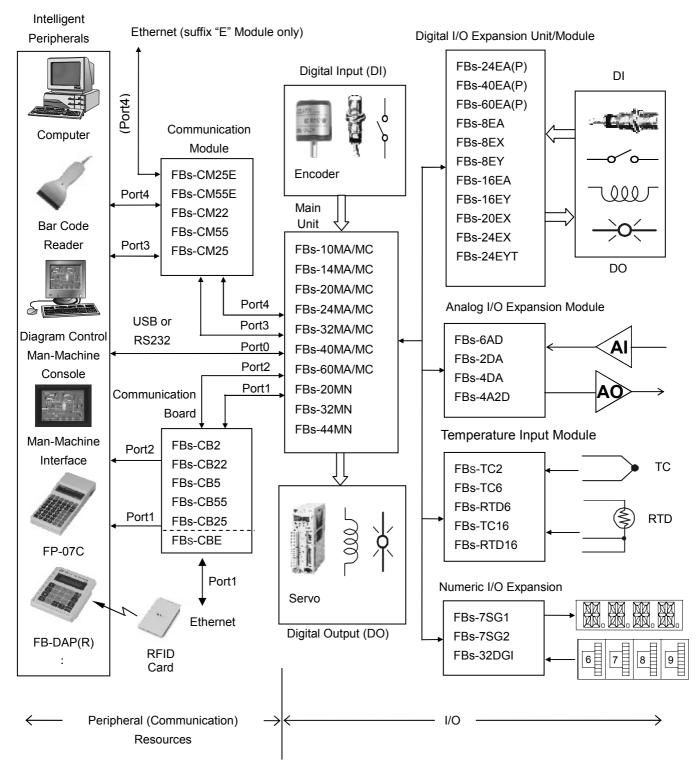

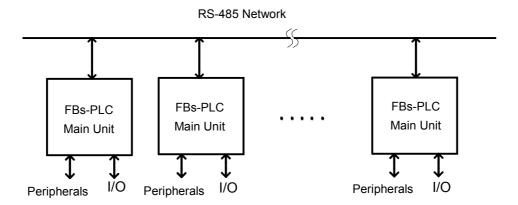

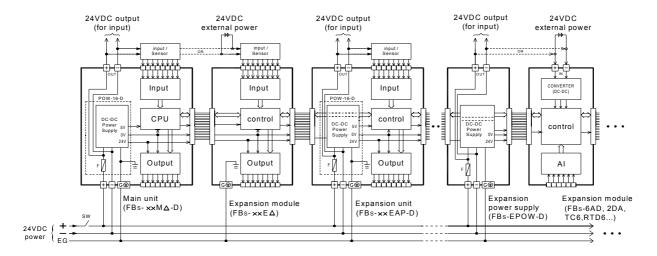

The FATEK FBs Series PLC is a new generation of micro PLC equipped with excellent functions comparable to medium or large PLC, with up to five communication ports. The maximum I/O numbers are 256 points for Digital Input (DI) and Digital Output (DO), 64 words for Numeric Input (NI) and Numeric Output (NO). The Main Units of FBs are available in three types: MA (Economy Type), MC (High-Performance Type), and MN (High-Speed NC Type). With the combination of I/O point ranges from 10 to 60, a total of 17 models are available. Fourteen DI/DO and 12 NI/NO models are available for Expansion Units/Modules. With interface options in RS232, RS485, USB and Ethernet, the communication peripherals are available with 14 boards and modules. The various models are described in the following:

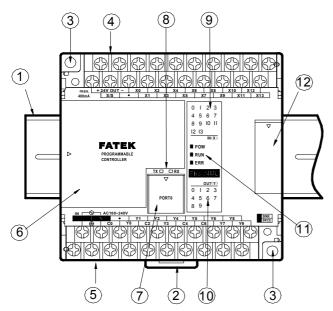

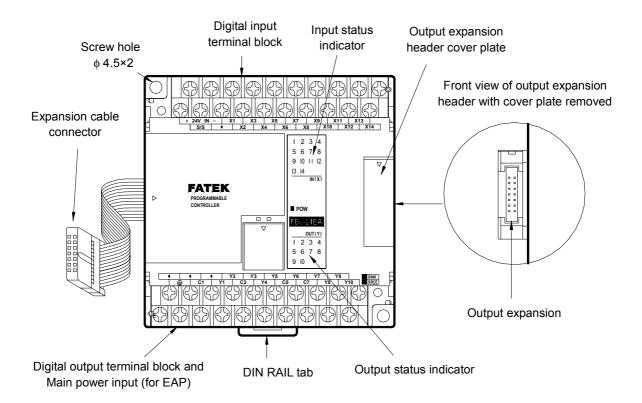

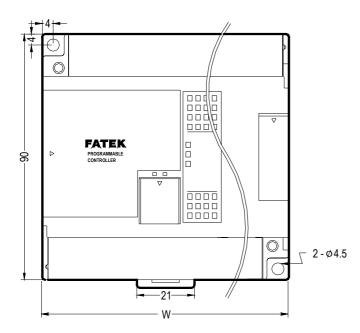

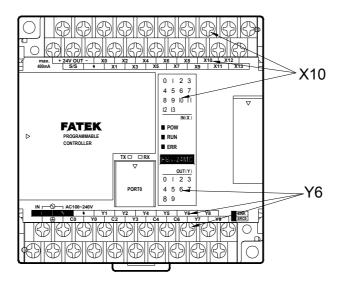

#### 1.1 Appearance of Main Unit

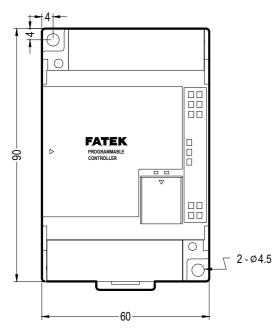

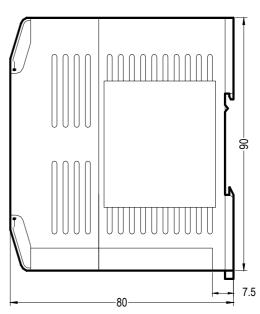

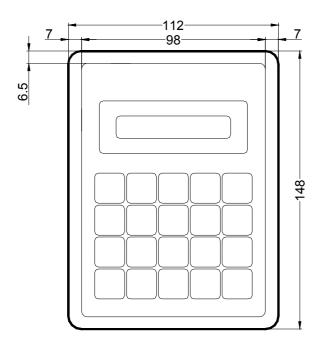

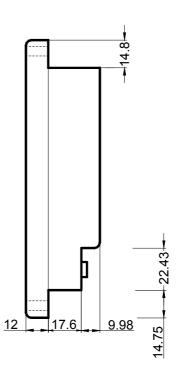

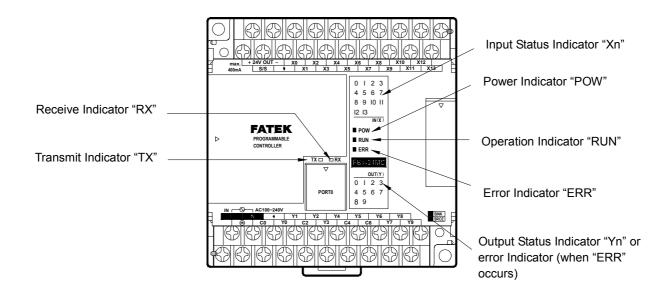

All the Main Units of FBs-PLC have the same physical structure. The only difference is the case width. There are four different case sizes, which are 60mm, 90mm, 130mm, and 175mm. The figure below will use the Main Unit case of the FBs-24MC as an example for illustration:

(Front view without Communication Board)

(Front view with cover plate removed)

(Front view with CB-22 Board installed)

- 35mm-width DIN RAIL

- 2 DIN RAIL tab

- $\bigcirc$  Hole for screw fixation ( $\phi 4.5 \times 2$ )

- 4 Terminals of 24VDC power input and digital input (Pitch 7.62mm)

- (Fitch 7.62mm)

- 6 Standard cover plate (without communication board)

- (Port 0) Cover plate of built-in communication port

- (RX) Indicators for transmit (TX) and receive (RX) status of built-in communication port (Port0).

- 9 Indicator for Digital Input (Xn).

- 10 Indicator for Digital Output (Yn).

- 11 Indicator for system status (POW, RUN, ERR).

- 1/O output expansion header cover [units of 20 points or beyond only], with esthetic purpose and capable of securing expansion cable.

- (CB).

- FBs-CB22 CB cover plate (each CB has its own specific cover plate)

- (15) Screw holes of communication board.

- (for CB2, CB22, CB5, CB55, and CB25)

- Connector for Communication Module (CM) (only available in MC/MN model, for CM22, CM25, CM55, CM25E, and CM55E connection).

- 18 Connector for Memory Pack.

- (9) Connector for built-in communication port (Port 0) (With USB and RS232 optional, shown in the figure is for RS232)

- 20 I/O output expansion header (only available in units with 20 points or beyond), for connecting with cables from expansion units/modules.

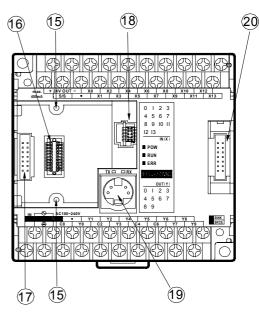

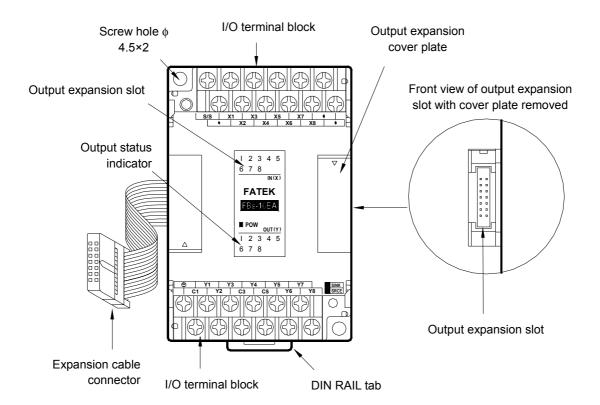

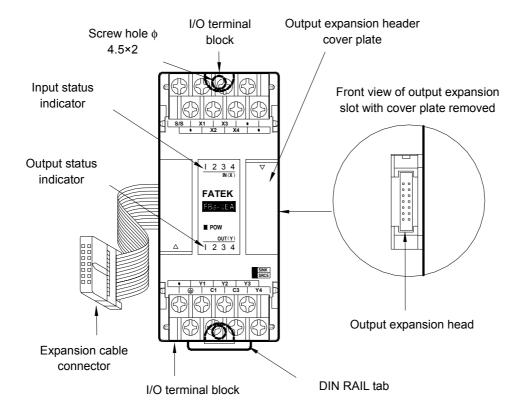

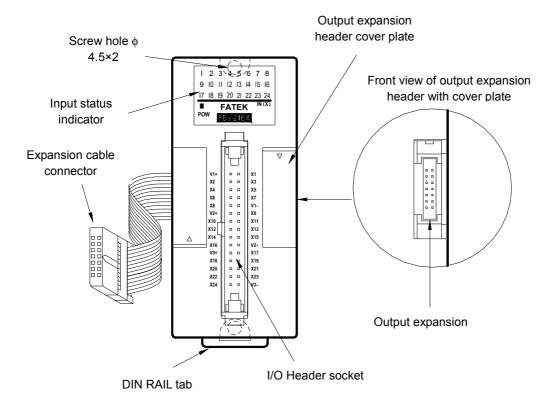

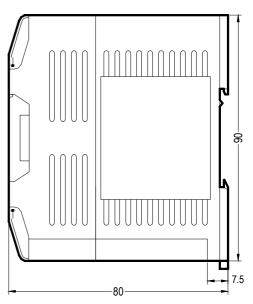

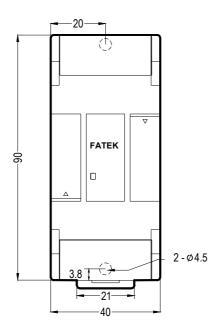

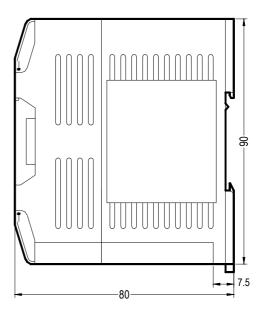

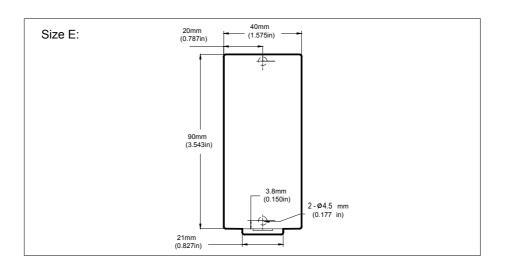

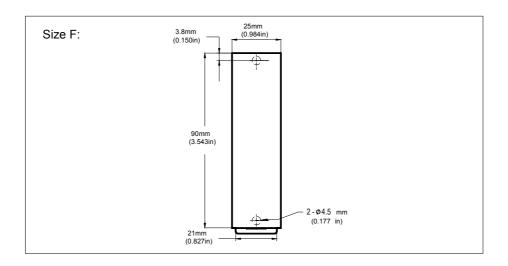

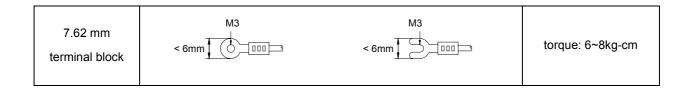

#### 1.2 Appearance of Expansion Unit/Module

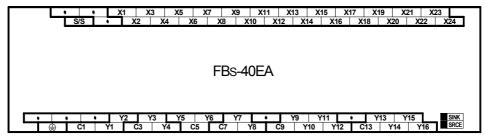

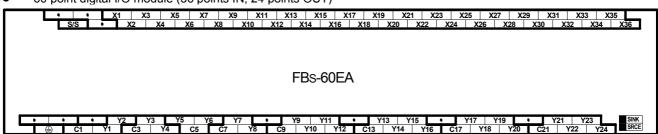

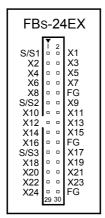

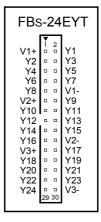

There are three types of cases for expansion units/modules. One type uses the same case as main unit that of the 90mm, 130mm, and 175mm, while the other two have thinner 40mm and 60mm cases, which are for expansion modules. All expansion cables (left) of expansion units/modules are flat ribbon cables (6cm long), which were soldered directly on the PCB, and the expansion header (right) is a 14Pin Header, with this to connect the right adjacent expansion units/modules. In the following, each of the three types of expansion units/modules is described as an example:

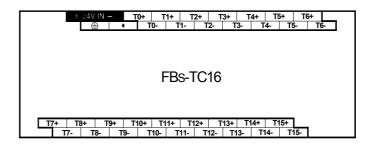

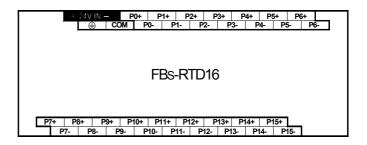

Expansion unit/module with 90mm, 130mm, or 175mm width case: [-24EA(P), -40EA(P), -60EA(P), -TC16,

-RTD16]

Expansion unit/module with 60mm width case: (-16EA, -16EY, -20EX)

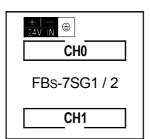

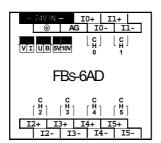

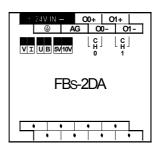

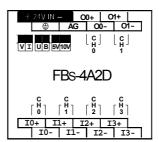

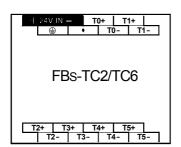

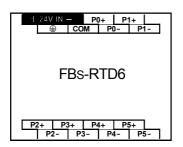

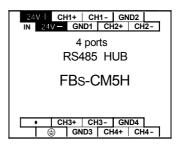

Expansion module with 40mm width case: (-8EA, -8EY, -8EX, -6AD, -2DA, -4DA, -4A2D, -7SG△, -TC2, -TC6, -RTD6, -CM5H)

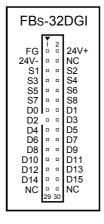

Expansion module with 40mm width case: (-24EX, -24EYT, -32DGI)

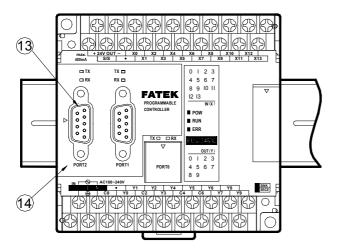

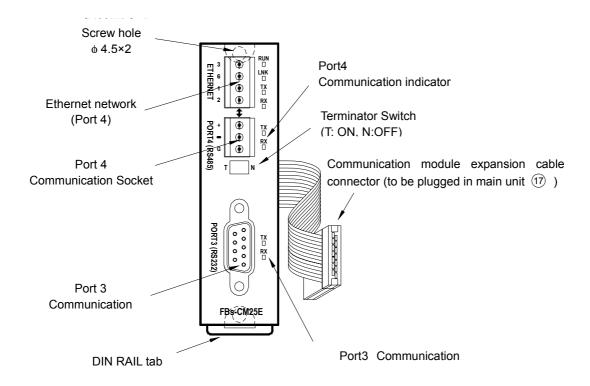

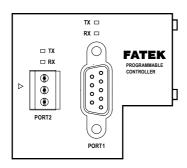

#### 1.3 Appearance of Communication Expansion Module

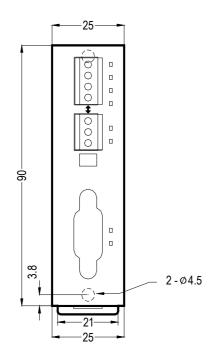

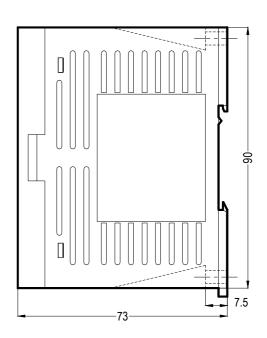

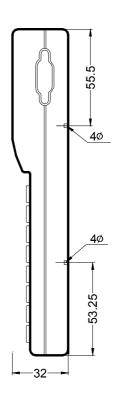

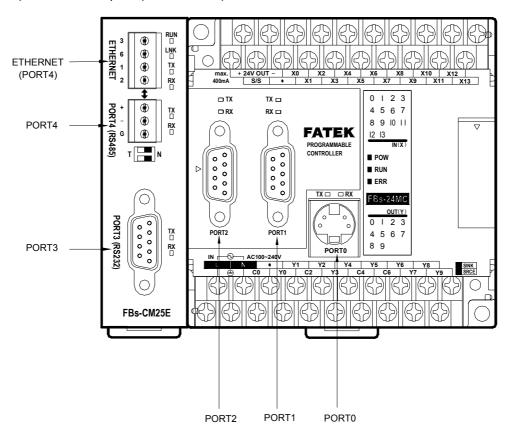

The Communication Module (CM) of FBs-PLC has a 25mm-width case, which can be used in the following seven modules: -CM22, -CM25, -CM55, -CM25E, -CM55E, -CM25C, -CM5R.

## 1.4 List of FBS PLC Models

|                    | Item Name           | Model Number                           | Specifications                                                                                                                                                                                              |

|--------------------|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

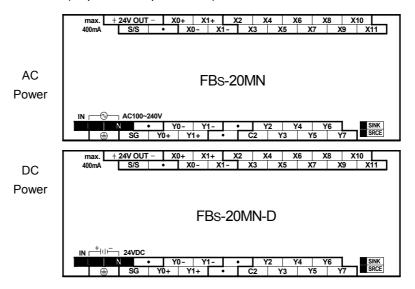

| Item Name          |                     | WOOGE WAITING                          | 2 points 7920KHz 5VDC differential input, 10 points 24VDC digital input (20KHz), 2 points 7920KHz                                                                                                           |

|                    |                     | FBs-20MN <u></u>                       | 5VDC differential output, 6 points (R/T/S) digital output (Model "T" 6 points 20KHz output), 1 RS232                                                                                                        |

| NC Control         |                     |                                        | or USB port (expandable up to 5), built-in RTC, detachable terminal block                                                                                                                                   |

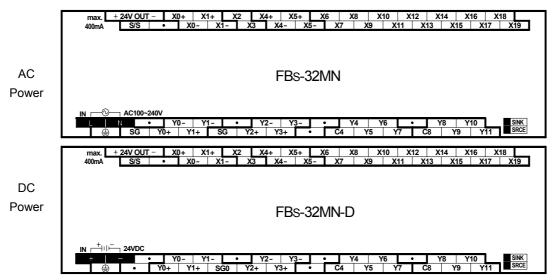

|                    |                     | <br>  FBs-32MN∏◊Δ - ⊚                  | 4 points 920KHz 5VDC digital differential input, 16 Points 24VDC digital input (20KHz for 12 Points), 4 points 7920KHz 5VDCdigital differential output, 8 Points (R/T/S) digital output (Model "T" 4 Points |

|                    | Main Unit           | 🗸 🕹                                    | 20KHz output), 1 RS232 or USB port (expandable up to 5), built-in RTC, detachable terminal block                                                                                                            |

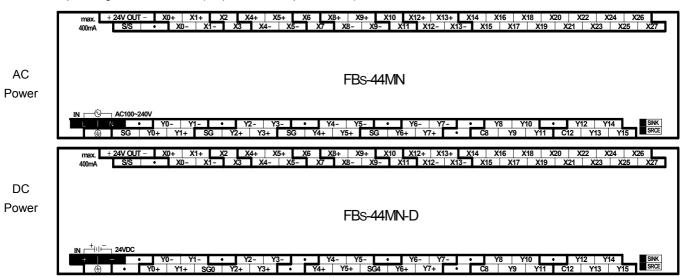

|                    |                     |                                        | 8 points 7920KHz 5VDC digital differential input, 20 Points 24VDC digital input (20KHz for 8 points),                                                                                                       |

|                    |                     | FBs-44MN                               | 8 points 7920KHz 5VDCdigital differential output, 8 points (R/T/S) digital output (Model "T" 4 Points 20KHz output), 1 RS232 or USB port (expandable up to 5), built-in RTC, detachable terminal block      |

|                    |                     |                                        | 6 points 24VDC digital input (2 points 100KHz+4 points 20KHz), 4 points (R/T/S) digital output                                                                                                              |

|                    |                     | FBs-10MC □◇∆ - ⊚ - XY                  | (Model "T" 2 points 100KHz+2 points 20KHz output), 1 RS232 or USB port (expandable up to 5),                                                                                                                |

|                    |                     |                                        | built-in RTC, I/O is not expandable  8 points 24VDC digital input (2 points 100KHz+6 points 20KHz), 6 points (R/T/S) digital output                                                                         |

|                    |                     | FBs-14MC                               | (Model "T" 2 points 100KHz+4 points 20KHz output), 1 RS232 or USB port (expandable up to 5),                                                                                                                |

|                    |                     |                                        | built-in RTC, I/O is not expandable                                                                                                                                                                         |

|                    |                     | <br>  FBs-20MC                         | 12 points 24VDC digital input (2 points 100KHz+10 points 20KHz), 8 points (R/T/S) digital output (Model "T" 2 points 100KHz+6 points 20KHz output), 1 RS232 or USB port (expandable up to 5),               |

|                    |                     |                                        | (Model "1" 2 points 100KHz+6 points 20KHz output), 1 RS232 or USB port (expandable up to 5), built-in RTC                                                                                                   |

|                    | Advanced            | ED 6:115                               | 14 points 24VDC digital input (2ppoints 100KHz+12 points 20KHz), 10 points (R/T/S) digital output                                                                                                           |

|                    | Main Unit           | FBs-24MC                               | (Model "T" 2 points 100KHz+6 points 20KHz output), 1 RS232 or USB port (expandable up to 5), built-in RTC, detachable terminal block                                                                        |

|                    |                     |                                        | 20 points 24VDC digital input (2 points 100KHz+14 points 20KHz), 12 Points (R/T/S) digital output                                                                                                           |

|                    |                     | FBs-32MC                               | (Model "T" 2 points 100KHz+6 points 20KHz output), 1 RS232 or USB port (expandable up to 5),                                                                                                                |

|                    |                     |                                        | built-in RTC, detachable terminal block  24 points 24VDC digital input (2 points 100KHz+14 points 20KHz), 16 points (R/T/S) digital output                                                                  |

|                    |                     | FBs-40MC                               | (24 points 24VDC digital input (2 points 100KHz+14 points 20KHz), 16 points (R/1/S) digital output (Model "T" 2 points 100KHz+6 points 20KHz output), 1 RS232 or USB port (expandable up to 5),             |

|                    |                     | _, _, ,                                | built-in RTC, detachable terminal block                                                                                                                                                                     |

|                    |                     | FBs-60MC                               | 36 points 24VDC digital input (2 points 100KHz+14 points 20KHz), 24 points (R/T/S) digital output                                                                                                           |

|                    |                     | TO-OOINIO□✓A - Ϣ - XY                  | (Model "T" 2 points 100KHz+6 points 20KHz output), 1 RS232 or USB port (expandable up to 5), built-in RTC, detachable terminal block                                                                        |

|                    |                     | FBs-10MA⊡◇∆ - ⊚                        | 6 points 24VDC digital input (up to 10KHz in 4 points), 4 Points (R/T/S) digital output (Model "T" has                                                                                                      |

|                    |                     | • •                                    | 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3), I/O is not expandable                                                                                                              |

|                    |                     | FBs-14MA□◇∆ - ⊚                        | 8 points 24VDC digital input (up to 10KHz in 4 points), 6 points (R/T/S) digital output (Model "T" has 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3), I/O is not expandable       |

|                    |                     | FBs-20MA □◇ △ - ◎                      | 12 points 24VDC digital input (up to 10KHz in 4 points), 8 points (R/T/S) digital output (Model "T"                                                                                                         |

|                    | Basic               |                                        | has 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3)                                                                                                                                 |

| ,                  | Basic<br>Main Unit  | FBs-24MA□◇∆ - ⊚                        | 14 points 24VDC digital input (up to 10KHz in 4 points), 10 points (R/T/S) digital output (Model "T" has 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3)                            |

|                    | VIII                | FBs-32MA                               | 20 points 24VDC digital input (up to 10KHz in 4 points), 12 points (R/T/S) digital output (Model "T"                                                                                                        |

|                    |                     |                                        | has 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3)                                                                                                                                 |

|                    |                     | FBS-40MA□◇∆ - ⊚                        | 24 points 24VDC digital input (up to 10KHz in 4 points), 16 points (R/T/S) digital output (Model "T" has 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3)                            |

|                    |                     | FBS-60MA □◇ Δ - ⊚                      | 36 points 24VDC digital input (up to 10KHz in 4 points), 24 points (R/T/S) digital output (Model "T"                                                                                                        |

| <u> </u>           | Type e == !         | . 50 00M/n_l\/ \( \Delta \ - \emptyset | has 4 points 10KHz output), one RS232 or USB port (can be expanded up to 3)                                                                                                                                 |

| E                  | Expansion<br>Power  | FBS-EPOW-⊚                             | Power supply for expansion module, with single 5VDC and dual 24VDC voltage output and up to 20VA capacity                                                                                                   |

|                    |                     | FBS-24EAP □ ♦ - ◎                      | 20VA capacity  14 points 24VDC digital input, 10 points (R/T/S) digital output, built-in power supply                                                                                                       |

|                    | Digital             | FBS-40EAP                              | 24 points 24VDC digital input, 10 points (R/1/S) digital output, built-in power supply                                                                                                                      |

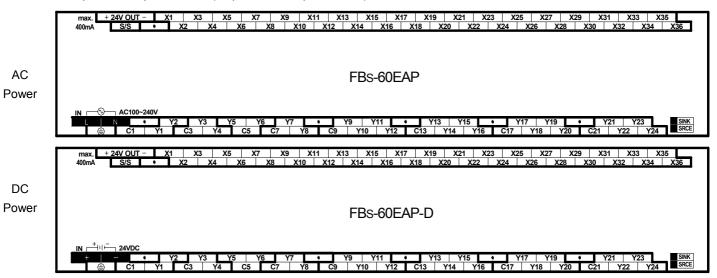

| Ex                 | pansion Unit        | FBS-60EAP □ ♦ - ◎                      | 36 points 24VDC digital input, 16 points (R/T/S) digital output, built-in power supply                                                                                                                      |

|                    |                     | FBS-8EA                                | 4 points 24VDC digital input, 4 points (R/T/S) digital output                                                                                                                                               |

|                    |                     | FBS-8EX                                | 8 points 24VDC digital input                                                                                                                                                                                |

|                    |                     | FBS-8EY□◇                              | 8 points (R/T/S) digital output                                                                                                                                                                             |

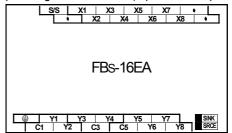

| <u>Di</u>          | Digital             | FBS-16EA□♦                             | 8 points 24VDC digital input, 8 points (R/T/S) digital output                                                                                                                                               |

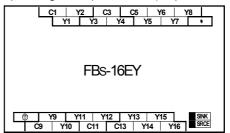

| Digital I/O Module | Expansion           | FBS-16EY□♦                             | 16 points (R/T/S) digital output                                                                                                                                                                            |

| /I  E              | Unit                | FBS-20EX                               | 20 points 24VDC digital input                                                                                                                                                                               |

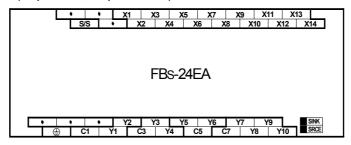

| 0                  |                     | FBS-24EA□◇                             | 14 points 24VDC digital input, 10 points (R/T/S) digital input                                                                                                                                              |

| ١٥                 |                     | FBS-40EA□◇                             | 24 points 24VDC digital input, 16 points (R/T/S) digital output                                                                                                                                             |

| lub                |                     | FBS-60EA□◇                             | 36 points 24VDCdigital input, 24 points (R/T/S) digital output                                                                                                                                              |

| е                  | High-Density        | FBS-24EX                               | 24 points high-density 24VDC digital input, 30-Pin Header with latch                                                                                                                                        |

| 1                  | Digital             |                                        |                                                                                                                                                                                                             |

| 1                  | Expansion<br>Module | FBS-24EYT                              | 24 points high-density transistor Sink type digital output (0.1A max.), 30-Pin Header with latch                                                                                                            |

| Щ.                 | iviodule            | <u> </u>                               |                                                                                                                                                                                                             |

|                                                                                                                                                                                   | Item Name                | Model Number                                                                                                                                                                                                                                                                                                                                                       | Specifications                                                                                                                                                                 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

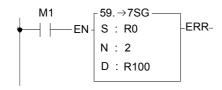

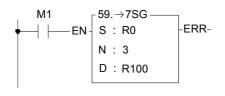

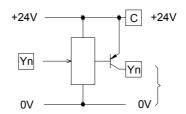

|                                                                                                                                                                                   |                          | FBs-7SG1                                                                                                                                                                                                                                                                                                                                                           | 1 set (8 digits) 7 segment LED display (or 64 Points independent LED) output display module,                                                                                   |  |  |

|                                                                                                                                                                                   | Numeric I/O<br>Expansion | FBs-7SG2                                                                                                                                                                                                                                                                                                                                                           | 16-Pin Header connector  2 set (16 digits) 7 segment LED display (or 128 Points independent LED) output display module,                                                        |  |  |

|                                                                                                                                                                                   | Module                   | FBs-32DGI                                                                                                                                                                                                                                                                                                                                                          | 16-Pin Header connector  8 set 4 digits (total 32 digits) Thumbwheel switch (or 128 Points independent switch) multiplex input module, 30-Pin Header connector                 |  |  |

| Numeric                                                                                                                                                                           |                          | FBs-6AD                                                                                                                                                                                                                                                                                                                                                            | 6 channel, 14 bits analog input module (-10V~0V~+10V or -20mA~0mA~+20mA)                                                                                                       |  |  |

| eri.                                                                                                                                                                              | Analog                   | FBs-2DA                                                                                                                                                                                                                                                                                                                                                            | 2 channel, 14 bits digital output module (-10V~0V~+10V or -20mA~0mA~+20mA)                                                                                                     |  |  |

| C                                                                                                                                                                                 | Expansion                | FBs-4DA                                                                                                                                                                                                                                                                                                                                                            | 4 channel, 14 bits digital output module (-10V~0V~+10V or -20mA~0mA~+20mA)                                                                                                     |  |  |

| /O M                                                                                                                                                                              | Module                   | FBs-4A2D                                                                                                                                                                                                                                                                                                                                                           | 4 channel, 14 bits analog input + 2 channel, 14 bits digital output combo analog module (-10V~0V~+10V or -20mA~0mA~+20mA)                                                      |  |  |

| Module                                                                                                                                                                            |                          | FBs-TC2                                                                                                                                                                                                                                                                                                                                                            | 2 channel thermocouple temperature input module with 0.1°C resolution                                                                                                          |  |  |

| ule                                                                                                                                                                               | Temperature              | FBs-TC6                                                                                                                                                                                                                                                                                                                                                            | 6 channel thermocouple temperature input module with 0.1°C resolution                                                                                                          |  |  |

|                                                                                                                                                                                   | Input                    | FBs-RTD6                                                                                                                                                                                                                                                                                                                                                           | 6 channel RTD temperature input module with 0.1°C resolution                                                                                                                   |  |  |

|                                                                                                                                                                                   | -                        | FBs-TC16                                                                                                                                                                                                                                                                                                                                                           | 16 channel thermocouple temperature input module with 0.1°C resolution                                                                                                         |  |  |

|                                                                                                                                                                                   | Wodule                   | FBs-RTD16                                                                                                                                                                                                                                                                                                                                                          | 16 channel RTD temperature input module with 0.1°C resolution                                                                                                                  |  |  |

|                                                                                                                                                                                   |                          | FBs-CM22                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                |  |  |

|                                                                                                                                                                                   |                          |                                                                                                                                                                                                                                                                                                                                                                    | 2 port RS232 (Port3+Port4) communication module                                                                                                                                |  |  |

|                                                                                                                                                                                   |                          | FBs-CM55                                                                                                                                                                                                                                                                                                                                                           | 2 port RS485 (Port3+Port4) communication module                                                                                                                                |  |  |

| Co                                                                                                                                                                                | mmunication              | FBs-CM25                                                                                                                                                                                                                                                                                                                                                           | 1 port RS232 (Port3)+1 port RS485 (Port4) communication module                                                                                                                 |  |  |

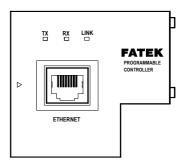

|                                                                                                                                                                                   | xpansion                 | FBs-CM25E                                                                                                                                                                                                                                                                                                                                                          | 1 port RS232 (Port3)+1 port RS485 (Port4)+ Ethernet network interface communication module                                                                                     |  |  |

| -                                                                                                                                                                                 | Module                   | FBs-CM55E                                                                                                                                                                                                                                                                                                                                                          | 1 port RS485 (Port3)+1 port RS485 (Port4)+ Ethernet network interface communication interface                                                                                  |  |  |

|                                                                                                                                                                                   |                          | FBs-CM25C                                                                                                                                                                                                                                                                                                                                                          | General purpose RS232 ← → RS485 Converter with optical isolation                                                                                                               |  |  |

|                                                                                                                                                                                   |                          | FBs-CM5R                                                                                                                                                                                                                                                                                                                                                           | General purpose RS485 Repeater with optical isolation                                                                                                                          |  |  |

|                                                                                                                                                                                   |                          | FBs-CM5H                                                                                                                                                                                                                                                                                                                                                           | General purpose 4-port RS485 HUB with optical isolation                                                                                                                        |  |  |

|                                                                                                                                                                                   |                          | FBs-CB2                                                                                                                                                                                                                                                                                                                                                            | 1 port RS232 (Port2) communication board                                                                                                                                       |  |  |

| <b>C</b> -                                                                                                                                                                        |                          | FBs-CB22                                                                                                                                                                                                                                                                                                                                                           | 2 port RS232 (Port1+Port2) communication board                                                                                                                                 |  |  |

|                                                                                                                                                                                   | mmunication<br>Expansion | FBs-CB5                                                                                                                                                                                                                                                                                                                                                            | 1 port RS485 (Port2) communication board                                                                                                                                       |  |  |

|                                                                                                                                                                                   | Board                    | FBs-CB55                                                                                                                                                                                                                                                                                                                                                           | 2 port RS485 (Port1+Port2) communication board                                                                                                                                 |  |  |

|                                                                                                                                                                                   | Board                    | FBs-CB25                                                                                                                                                                                                                                                                                                                                                           | 1 port RS232 (Port1)+1 port RS485 (Port2) communication board                                                                                                                  |  |  |

|                                                                                                                                                                                   |                          | FBs-CBE                                                                                                                                                                                                                                                                                                                                                            | 1 port Ethernet communication board                                                                                                                                            |  |  |

| Co                                                                                                                                                                                | mmunication              | FBs-232P0-9F-150                                                                                                                                                                                                                                                                                                                                                   | FBs-Main unit Port0 RS232 to 9Pin female D-Sub communication cable, 150cm long                                                                                                 |  |  |

|                                                                                                                                                                                   | Cable                    | FBs-232P0-9M-400                                                                                                                                                                                                                                                                                                                                                   | FBs-Main unit Port0 RS232 to 9Pin male D-Sub communication cable, 400cm long FBs-Main unit Port0 USB communication cable (standard USB A ← → B)                                |  |  |

|                                                                                                                                                                                   |                          | FBs-USBP0-180                                                                                                                                                                                                                                                                                                                                                      | FBs-Main unit Portu USB communication cable (standard USB A $\longleftrightarrow$ B)  FBs-PLC Program memory pack with 20Kword program, 20Kword register, and write protection |  |  |

| Me                                                                                                                                                                                | emory Pack               | FBs-PACK                                                                                                                                                                                                                                                                                                                                                           | switch                                                                                                                                                                         |  |  |

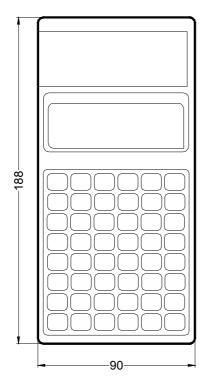

| Pr                                                                                                                                                                                | ogramming                | FP-07C                                                                                                                                                                                                                                                                                                                                                             | Hand held programmer for FBs-PLC                                                                                                                                               |  |  |

|                                                                                                                                                                                   | Device                   | WinProladder                                                                                                                                                                                                                                                                                                                                                       | WinProladder Programming software for Windows                                                                                                                                  |  |  |

|                                                                                                                                                                                   |                          | FATEK Comm. Server                                                                                                                                                                                                                                                                                                                                                 | FATEK DDE communication server                                                                                                                                                 |  |  |

|                                                                                                                                                                                   | Others                   | FBs-XTNR                                                                                                                                                                                                                                                                                                                                                           | Extension cable adapter  Include 22AWG I/O cable for 30Pin Header connector, 200cm long ( for FBs-24EX, -24EYT, and                                                            |  |  |

|                                                                                                                                                                                   |                          | HD30-22AWG-200                                                                                                                                                                                                                                                                                                                                                     | -32DGI)                                                                                                                                                                        |  |  |

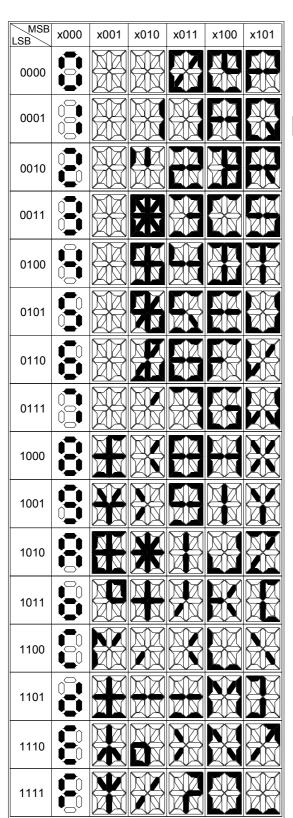

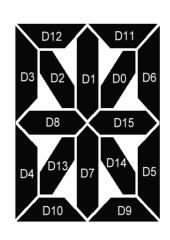

|                                                                                                                                                                                   |                          | DBAN.8(DBAN.8LEDR)                                                                                                                                                                                                                                                                                                                                                 | 0.8 "×4 16 segment display board (with red LED installed )                                                                                                                     |  |  |

| 16                                                                                                                                                                                | " Ocgilicit              | DBAN2.3(DBAN2.3LEDR)                                                                                                                                                                                                                                                                                                                                               | 2.3 *×4 16 segment display board (with red LED installed )                                                                                                                     |  |  |

|                                                                                                                                                                                   |                          | DB.56 (DB.56LEDR)                                                                                                                                                                                                                                                                                                                                                  | 0.56 " ×8 7 segment display board (with red LED installed)                                                                                                                     |  |  |

| Display Board                                                                                                                                                                     |                          | DB.8 (DB.8LEDR)                                                                                                                                                                                                                                                                                                                                                    | 0.8 *×8 7 segment display board (with red LED installed)                                                                                                                       |  |  |

|                                                                                                                                                                                   |                          | DB2.3 (DB2.3LEDR) DB4.0 (DB4.0LEDR)                                                                                                                                                                                                                                                                                                                                | 2.3 * ×8 7 segment display board (with red LED installed) 4.0 * ×4 7 segment display board (with red LED installed)                                                            |  |  |

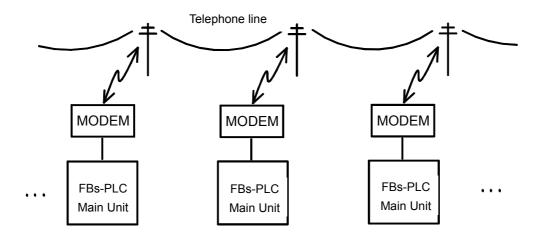

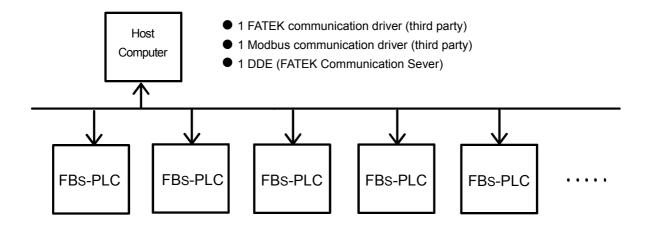

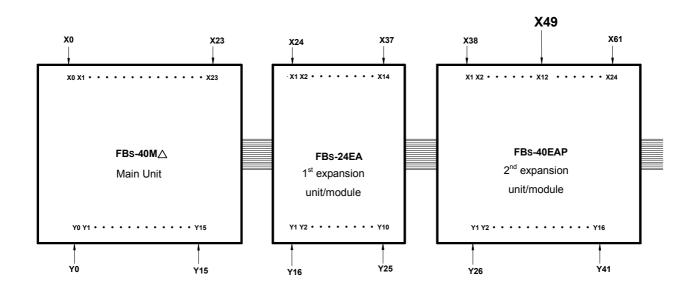

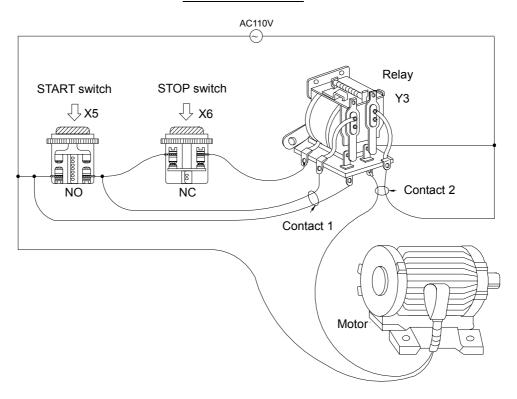

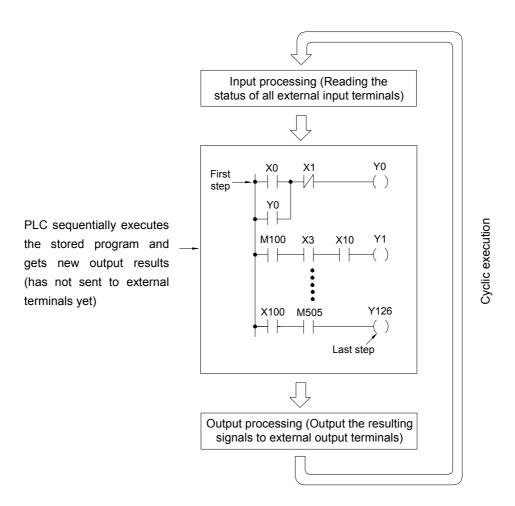

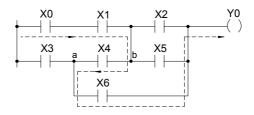

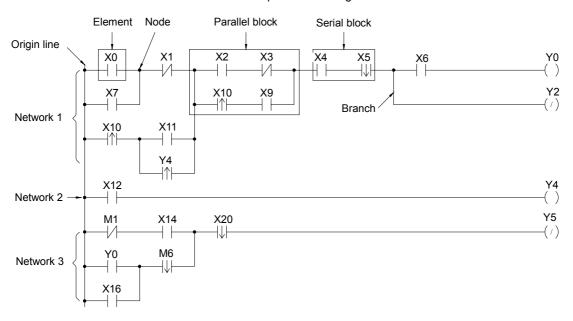

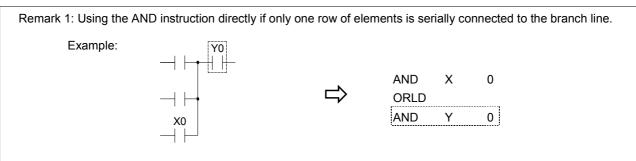

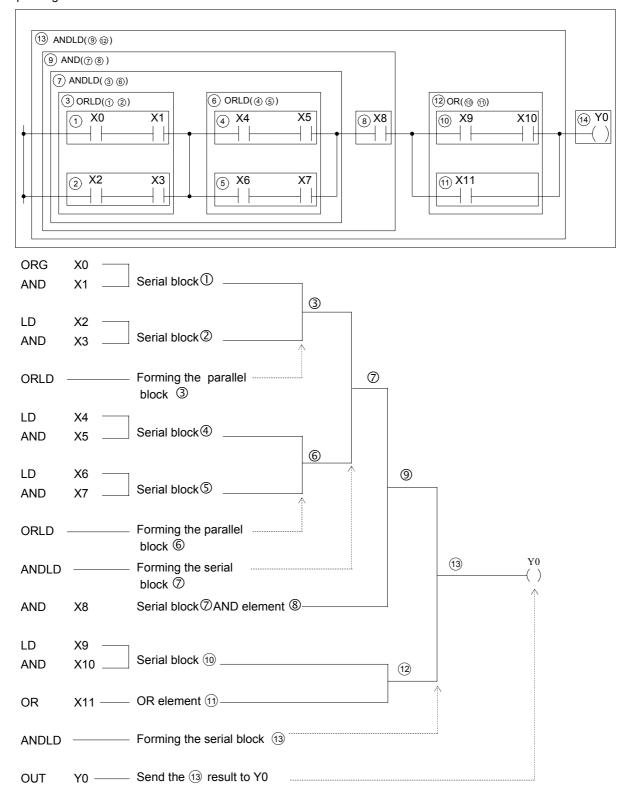

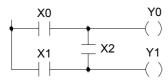

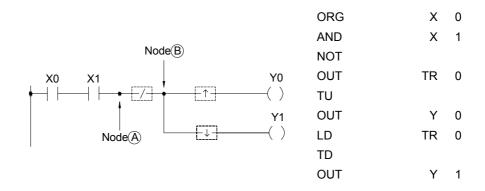

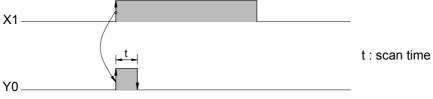

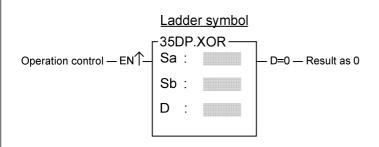

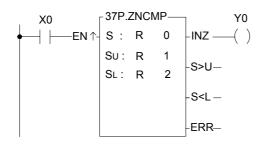

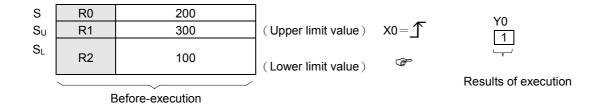

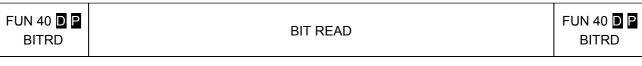

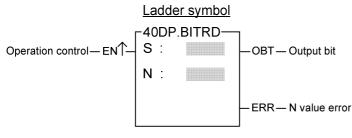

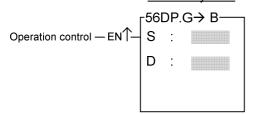

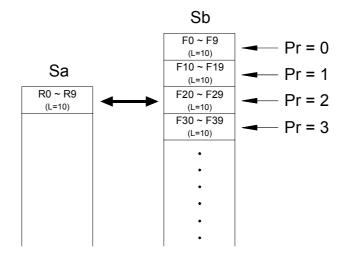

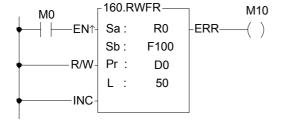

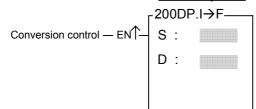

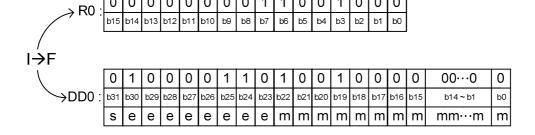

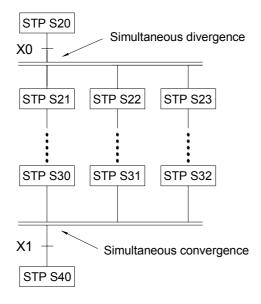

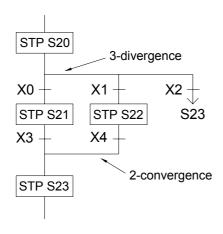

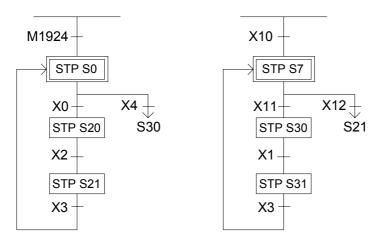

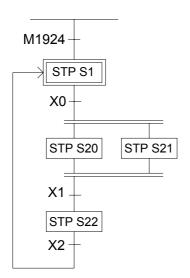

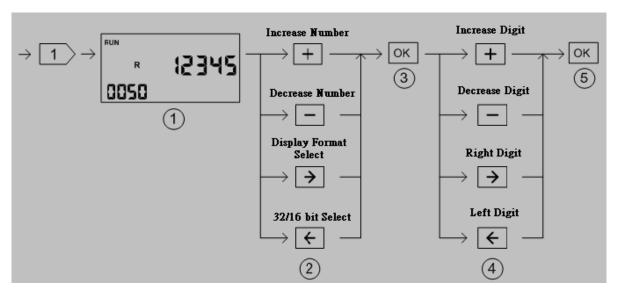

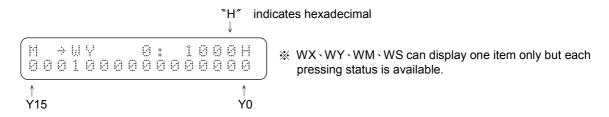

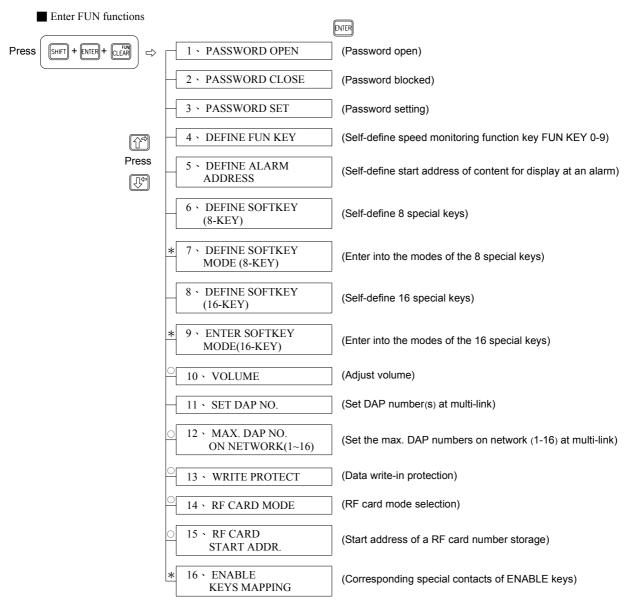

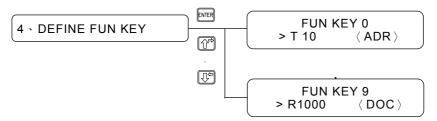

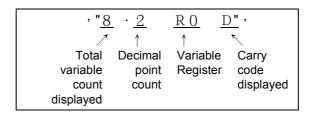

| Cimula Danula                                                                                                                                                                     |                          | ` '                                                                                                                                                                                                                                                                                                                                                                | 16×2 LCD character display, 20key keyboard, 24VDC power supply, RS-485 communication                                                                                           |  |  |